#### ABSTRACT

Title of Document: DISK DESIGN-SPACE EXPLORATION IN TERMS OF SYSTEM-LEVEL PERFORMANCE, POWER, AND ENERGY CONSUMPTION Nuengwong Tuaycharoen Doctor of Philosophy, 2006

Directed By: Associate Professor Bruce L. Jacob Department of Electrical and Computer Engineering University of Maryland, College Park

To make the common case fast, most studies focus on the computation phase of applications in which most instructions are executed. However, many programs spend significant time in the I/O intensive phase due to the I/O latency. To obtain a system with more balanced phases, we require greater insight into the effects of the I/O configurations to the entire system in both performance and power dissipation domains.

Due to lack of public tools with the complete picture of the entire memory hierarchy, we developed SYSim. SYSim is a complete-system simulator aiming at complete memory hierarchy studies in both performance and power consumption domains. In this dissertation, we used SYSim to investigate the system-level impacts of several disk enhancements and technology improvements to the detailed interaction in memory hierarchy during the I/O-intensive phase. The experimental results are reported in terms of both total system performance and power/energy consumption. With SYSim, we conducted the complete-system experiments and revealed intriguing behaviors including, but not limited to, the following:

- During the I/O intensive phase which consists of both disk reads and writes, the average system CPI tracks only average disk read response time, and not overall average disk response time, which is the widely-accepted metric in disk drive research.

- In disk read-dominating applications, Disk Prefetching is more important than increasing the disk RPM. On the other hand, in applications with both disk reads and writes, the disk RPM matters.

- The execution time can be improved to an order of magnitude by applying some disk enhancements. Using disk caching and prefetching can improve the performance by the factor of 2, and write-buffering can improve the performance by the factor of 10. Moreover, using disk caching/prefetching and the write-buffering techniques in conjunction can improve the total system performance by at least an order of magnitude.

- Increasing the disk RPM and the number of disks in RAID disk system also have an impressive improvement over the total system performance.

However, employing such techniques requires careful consideration for tradeoffs in power/energy consumption.

# DISK DESIGN-SPACE EXPLORATION IN TERMS OF SYSTEM-LEVEL PERFORMANCE, POWER, AND ENERGY CONSUMPTION

By

Nuengwong Tuaycharoen

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park, in partial fulfillment of the requirements for the degree of Doctor of Philosophy 2006

Advisory Committee: Associate Professor Bruce Jacob, Chair Associate Professor Manoj Franklin Associate Professor Gang Qu Assistant Professor Ankur Srivastava Professor Lawrence Washington © Copyright by Nuengwong Tuaycharoen 2006

## **Table of Contents**

| <b>Chapter 1: Introduction</b> | 1 |

|--------------------------------|---|

|--------------------------------|---|

| 1.1 | Problem Description           | . 1 |

|-----|-------------------------------|-----|

|     | Contribution and Significance |     |

| 1.3 | Organization of Dissertation  | 14  |

### Chapter 2: Memory Hierarchy ......15

| 2.1 | Memory Hierarchy                                                | 16 |

|-----|-----------------------------------------------------------------|----|

| 2.2 | Virtual Memory                                                  | 17 |

| 2.3 | Caches                                                          | 19 |

|     | 2.3.1. Cache Memory Cell                                        | 20 |

|     | 2.3.2. Cache Operations                                         |    |

|     | 2.3.3. CACTI: An Integrated Cache Timing, Power, and Area Model |    |

|     | 2.3.4. Wattch                                                   |    |

| 2.4 | Main Memory: DRAM                                               | 34 |

|     | 2.4.1. DRAM Memory Cell                                         |    |

|     | 2.4.2. Standard DRAM Device                                     |    |

|     | 2.4.3. DRAM-Based Memory System Organization                    |    |

|     | 2.4.4. DRAM Commands                                            |    |

|     | 2.4.5. Memory Controller                                        | 50 |

|     |                                                                 |    |

###

| 3.1 | Classifications of Disk Drives | 57 |

|-----|--------------------------------|----|

| 3.2 | Areal Density Growth Trend     | 59 |

| 3.3 | Performance Metrics            | 61 |

|     | 3.3.1. Command overhead        |    |

|     | 3.3.2. Seek time               |    |

|     | 3.3.3. Rotational latency                           | 64 |

|-----|-----------------------------------------------------|----|

|     | 3.3.4. Data transfer time                           | 64 |

| 3.4 | The Physical Layer                                  | 65 |

|     | 3.4.1. Principles of Rotating Storage Devices       | 65 |

|     | 3.4.2. Magnetic Recording                           | 67 |

|     | 3.4.3. Mechanical and Magnetic Components           |    |

|     | 3.4.4. Electronics                                  | 76 |

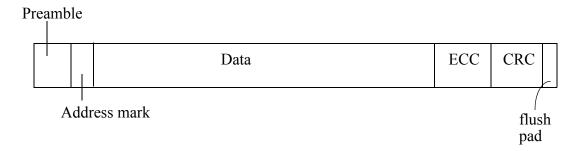

| 3.5 | The Data Layer                                      | 79 |

|     | 3.5.1. Disk Blocks or Sectors                       | 80 |

|     | 3.5.2. Tracks                                       |    |

|     | 3.5.3. Cylinders                                    |    |

|     | 3.5.4. Address Mapping                              |    |

|     | 3.5.5. Internal Addressing                          |    |

|     | 3.5.6. External Addressing                          |    |

|     | 3.5.7. Logical Address to Physical Location Mapping |    |

|     | 3.5.8. Zoned Bit Recording                          | 85 |

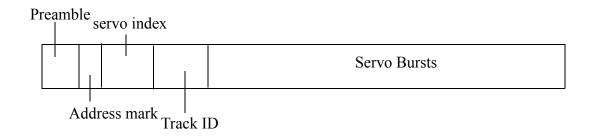

|     | 3.5.9. Servo                                        |    |

|     | 3.5.10. Sector ID and No-ID Formatting              |    |

|     | 3.5.11. Defect Management                           |    |

| 3.6 | File System Caching                                 |    |

|     |                                                     |    |

## Chapter 4: Related Work ......99

| 4.1 | Complete-System Simulations                                | . 99 |

|-----|------------------------------------------------------------|------|

| 4.2 | Magnetic Disk Drive Enhancements and Physical Improvements | 105  |

|     | 4.2.1. Disk Drive Enhancements                             | 107  |

|     | 4.2.2. Disk Drive Physical Improvements                    | 119  |

|     |                                                            |      |

## Chapter 5: Methodology .....124

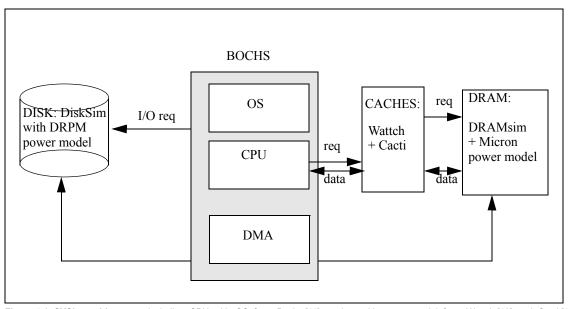

| The Processor Simulator: Bochs         | 126                                                                                                                              |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| The Cache Simulator: Wattch            | 127                                                                                                                              |

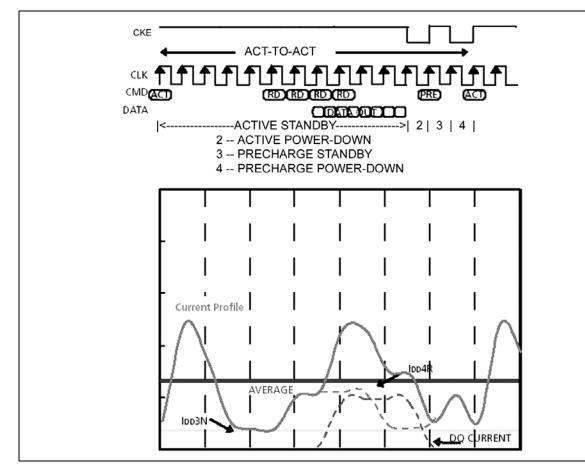

| The DRAM Simulator and Its Power Model | 129                                                                                                                              |

| The Disk Simulator: DiskSim            | 137                                                                                                                              |

| The Benchmarks: SPEC2000               | 139                                                                                                                              |

| Interactions                           | 140                                                                                                                              |

|                                        | The Cache Simulator: Wattch<br>The DRAM Simulator and Its Power Model<br>The Disk Simulator: DiskSim<br>The Benchmarks: SPEC2000 |

| 5.7 | Parameter and Benchmark Selections | 145 |

|-----|------------------------------------|-----|

| 5.8 | SYSim and Real Systems Comparison  | 151 |

| 5.9 | Sample Output                      | 154 |

## Chapter 6: Experimental Results ......159

| 6.1 | I/O intensive phase                                     | 159         |

|-----|---------------------------------------------------------|-------------|

| 6.2 | Memory Size and I/O Behaviors                           |             |

| 6.3 | Power/Energy Consumption of the Disk due to Different M | Memory Size |

|     |                                                         |             |

| 6.4 | Effects of Disk Physical Technology Improvement and Er  |             |

|     |                                                         |             |

|     | 6.4.1. Rotational Speed (RPM)                           |             |

|     | 6.4.2. Prefetching                                      |             |

|     | 6.4.3. Parallel I/O: RAID5                              |             |

|     | 6.4.4. Size of the Disk Cache                           |             |

|     | 6.4.5. Disk Cache Organization                          |             |

|     | 6.4.6. Bus Transmission Latency                         |             |

|     | 6.4.7. Perfect Write-Buffering                          | 214         |

| 6.5 | Total CPI v.s. Disk Response Time                       | 221         |

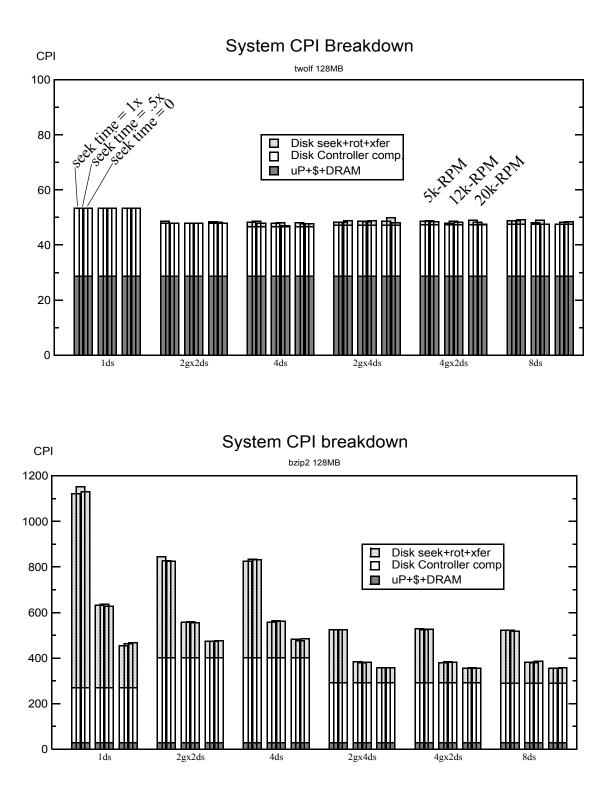

| 6.6 | The CPI Breakdown                                       | 223         |

| 6.7 | Power/Energy Consumption                                | 225         |

| 6.8 | The System Bandwidth                                    | 237         |

| 6.9 | Configuration Comparison                                | 239         |

| Chapter 7: Conclusions | 245 |

|------------------------|-----|

| Appendix: SPEC CPU2000 | 250 |

| References             |     |

## **List of Tables**

| Table 1.1: | Execution Time Breakdown for System #1: 750MHz CPU with 96MB memory                                                                 | 1    |

|------------|-------------------------------------------------------------------------------------------------------------------------------------|------|

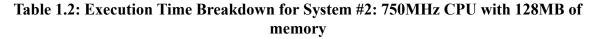

| Table 1.2: | Execution Time Breakdown for System #2: 750MHz CPU with 128MH memory                                                                | 3 of |

| Table 2.1: | CACTI input parameters                                                                                                              |      |

| Table 2.2: | CACTI output implementation parameters                                                                                              | 28   |

| Table 4.1: | Attributes of various performance modeling techniques [3]                                                                           | 100  |

| Table 4.2: | Latest Disk Interfaces and Their Data Rate                                                                                          | 123  |

| Table 5.1: | The definitions of symbols in the DRAM datasheet                                                                                    | 130  |

| Table 5.2: | Base Configuration for CPU, caches, and memory                                                                                      | 146  |

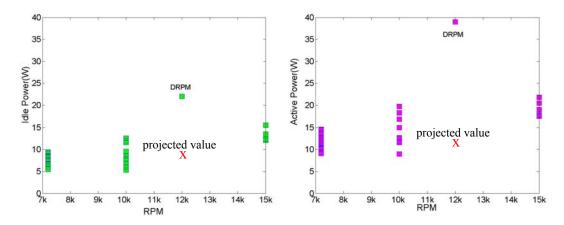

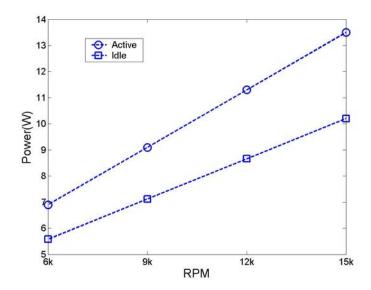

| Table 5.3: | Disk Active and Idle Power Values                                                                                                   | 149  |

| Table 5.4: | Execution Time Breakdown for System #1: 750MHz CPU with 96MB memory                                                                 | 151  |

| Table 5.5: | Execution Time Breakdown for System #2: 750MHz CPU with 128MH memory comparing with a SYSim system with 2GHz CPU with 128M memory.  | 3 of |

| Table 5.6: | Execution Time Breakdown for System #3: 2.4GHz CPU with 1GB of memory comparing with a SYSim system with 2GHz CPU with 512M memory. |      |

# **List of Figures**

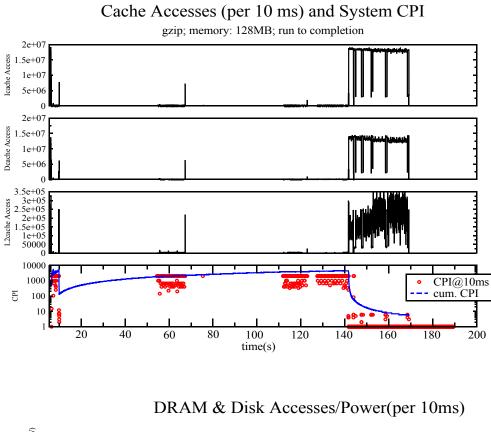

| Figure 1.1:  | The System CPI                                                      | 3   |

|--------------|---------------------------------------------------------------------|-----|

| Figure 2.1:  | Memory Hierarchy in Typical Computer Systems                        |     |

| Figure 2.2:  | The basic SRAM cellsix-transistor memory cell(6T MC)                |     |

| Figure 2.3:  | Block Diagram of a 2-way set associative cache organization,        |     |

| Figure 2.4:  | Cache structure                                                     |     |

| Figure 2.5:  | Schematic of wordlines and bitlines in Wattch array structure [19]  | 32  |

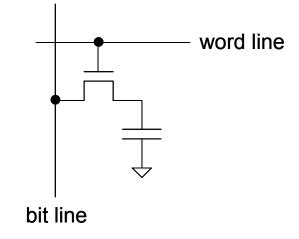

| Figure 2.6:  | a DRAM memory cellone transistor one capacity (1T1C)                | 35  |

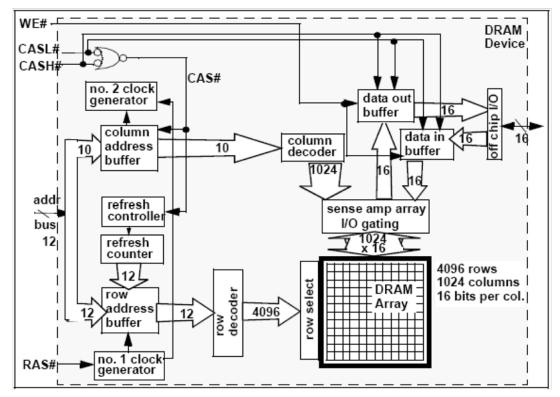

| Figure 2.7:  | 64 Mbit Fast Page Mode DRAM Device (4096 x 1024 x 16) [17]          | 37  |

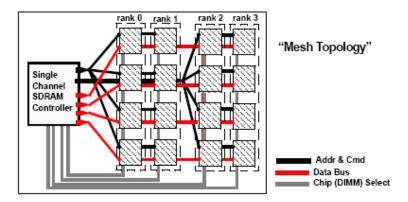

| Figure 2.8:  | The Classic Memory Topology [17]                                    | 42  |

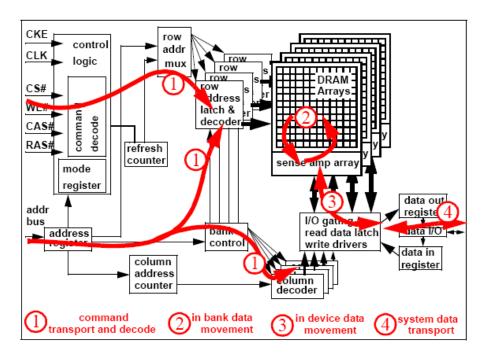

| Figure 2.9:  | Command and data movement on generic SDRAM device. [17]             | 44  |

| Figure 3.1:  | Basic Data Organization of a disk drive                             | 79  |

| Figure 3.2:  | Components of a sector                                              | 81  |

| Figure 3.3:  | Components of a servo sector                                        | 92  |

| Figure 5.1:  | SYSim architecture                                                  | 124 |

| Figure 5.2:  | Read Current with I/O Power Included [18].                          | 132 |

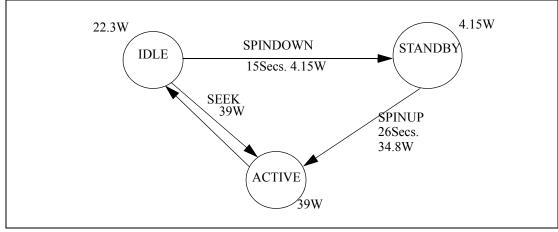

| Figure 5.3:  | TPM Power Modes [15]                                                | 138 |

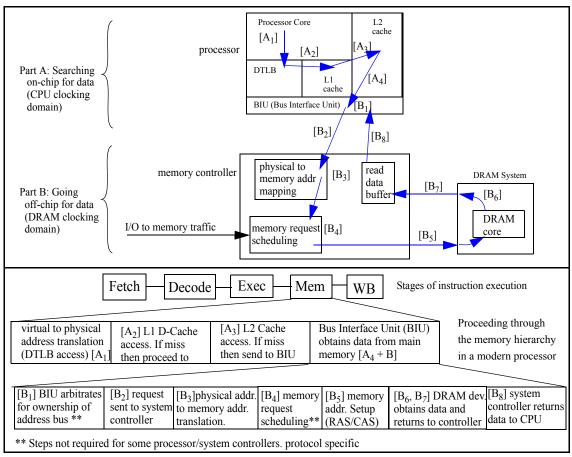

| Figure 5.4:  | : Abstract Illustration of a Load Instruction in a Processor-Memory |     |

|              | System [17]                                                         | 141 |

| Figure 5.5:  | Idle and Active Power of 47 Commercially Available Disk drives      | 148 |

| Figure 5.6:  | Son and Kandemir's Disk Power Projection for IBM Ultrastar 36Z15.   | 149 |

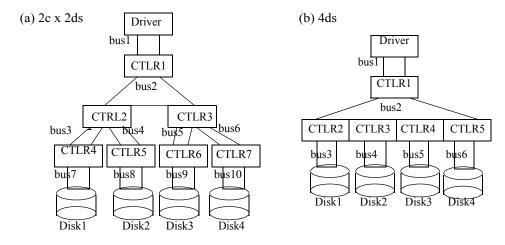

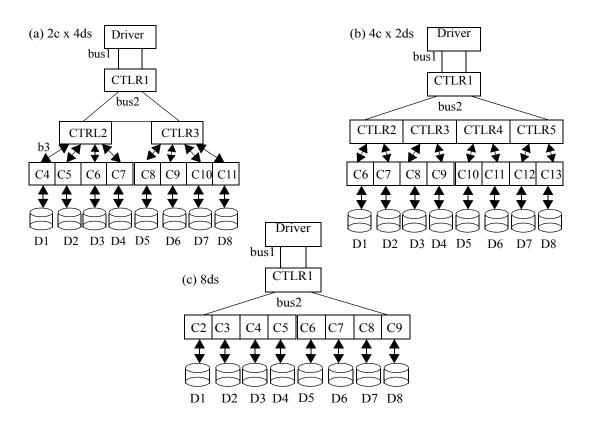

| Figure 5.7:  | (1) RAID5 Configuration for an 4-disk system                        | 150 |

| Figure 5.7:  | (2) RAID5 Configuration for an 8-disk system                        | 150 |

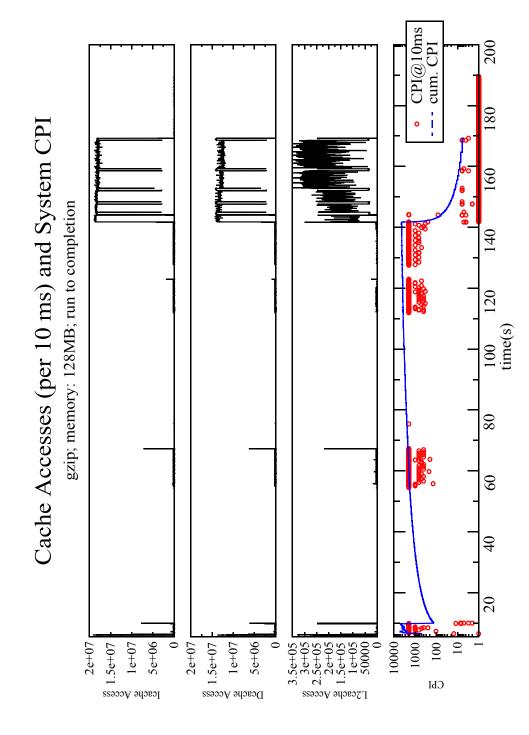

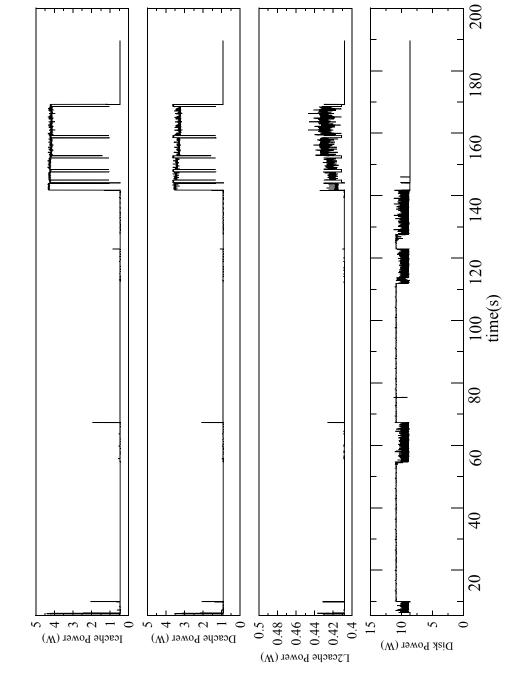

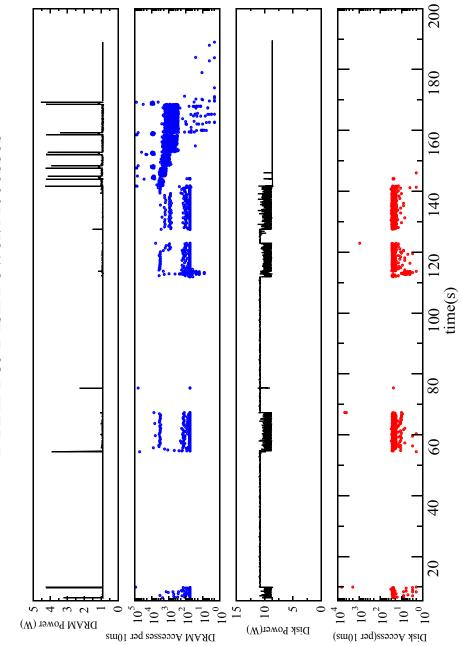

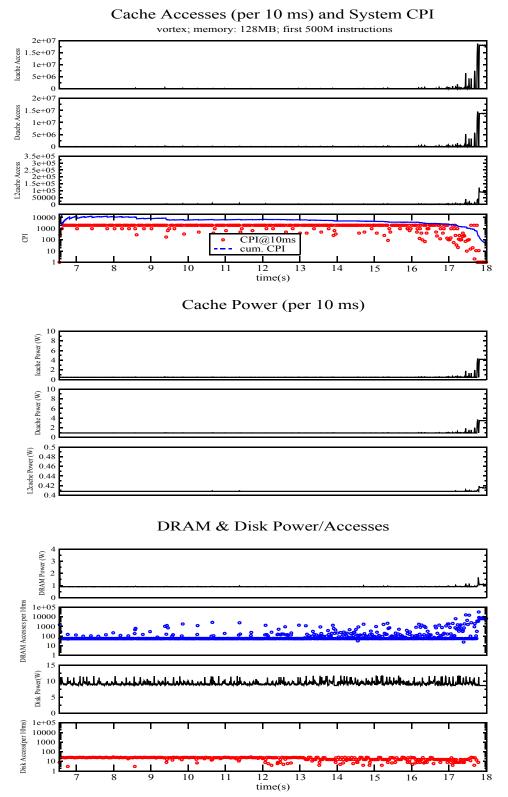

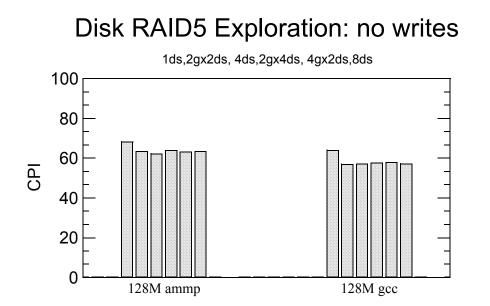

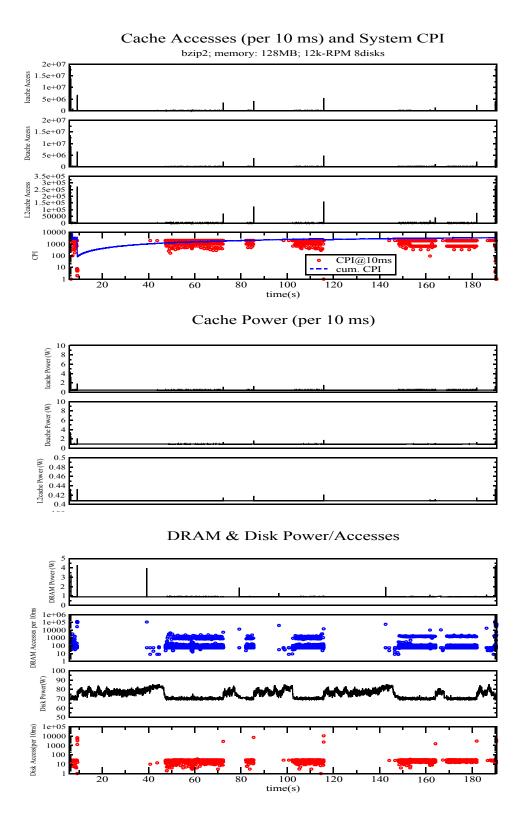

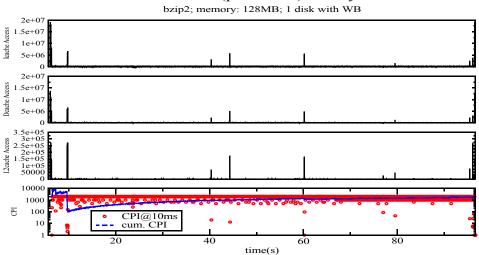

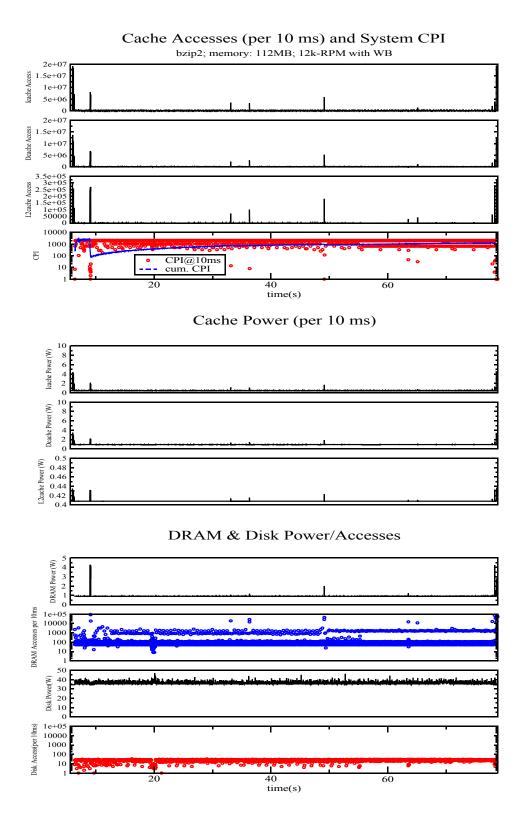

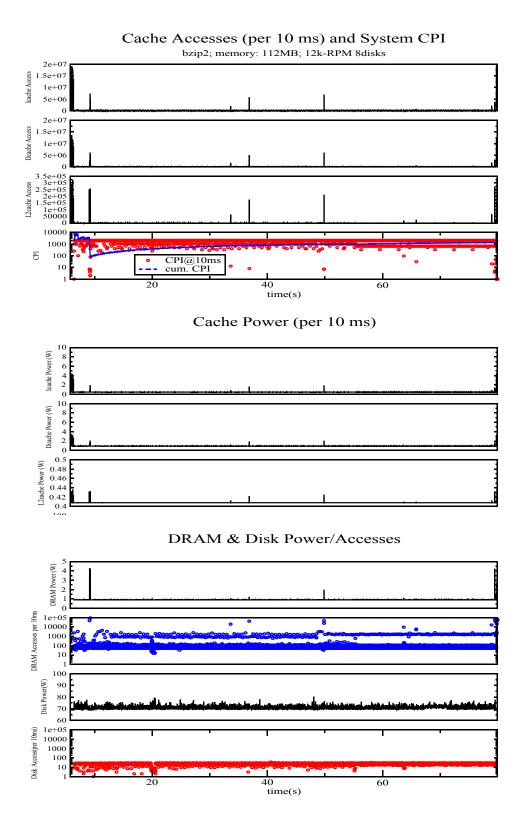

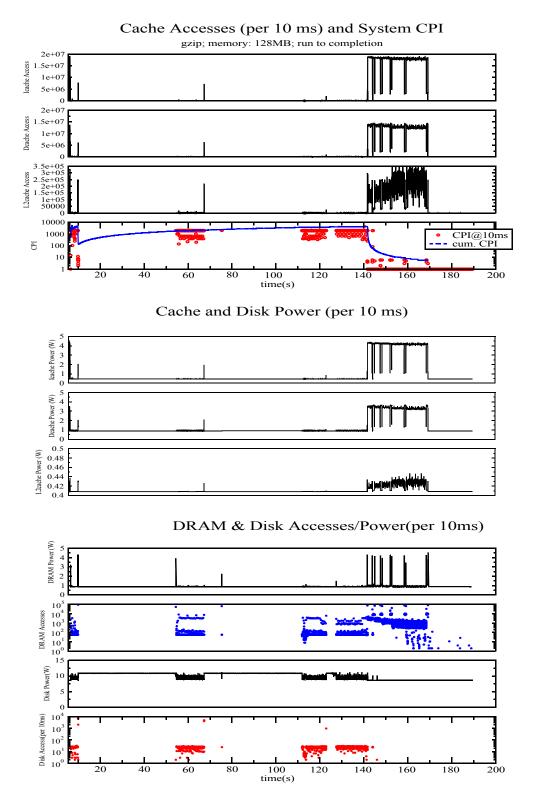

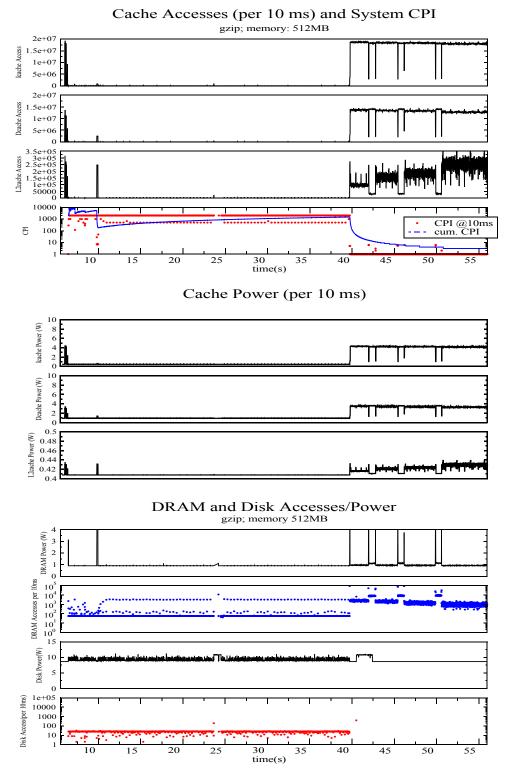

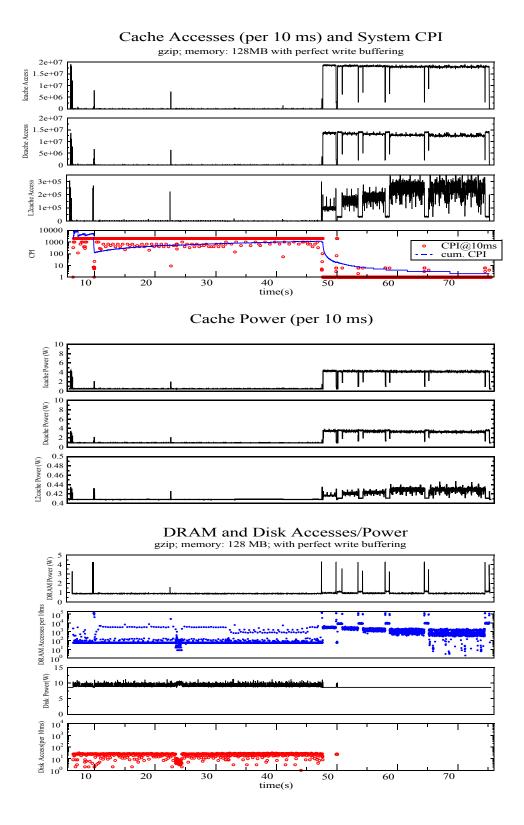

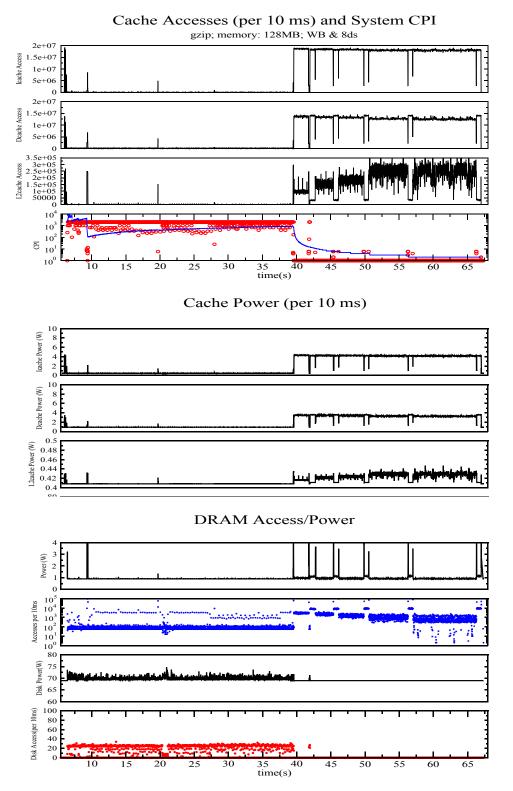

| Figure 5.8:  | Sample Output of Cache Accesses and Total system CPI                | 155 |

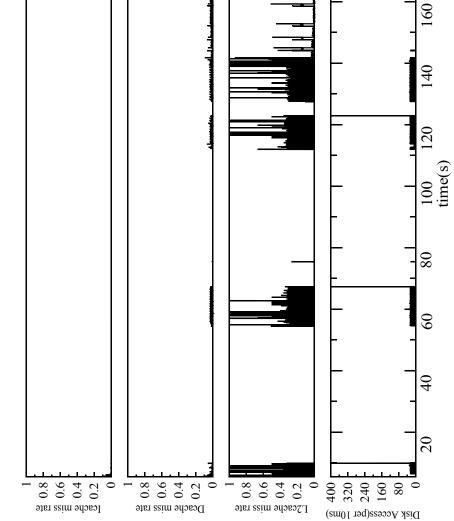

| Figure 5.9:  | Sample Output of Cache miss rate and Disk Accesses                  | 156 |

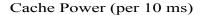

| Figure 5.10: | Sample Output of Cache power and Disk Power Dissipation             | 157 |

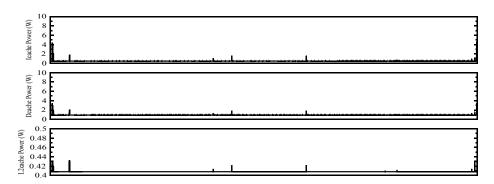

| Figure 5.11: | Sample Output of DRAM and Disk Accesses and Power                   | 158 |

| Figure 6.1:  | The System CPI                                                      | 160 |

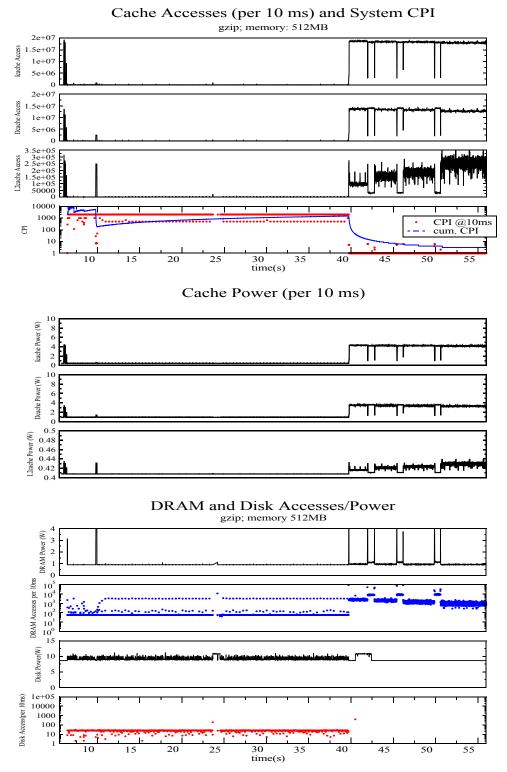

| Figure 6.2:  | The interaction in memory hierarchy in a system with 512MB of mem   | •   |

| Eigung (2)   | I/O intensive above of amount                                       |     |

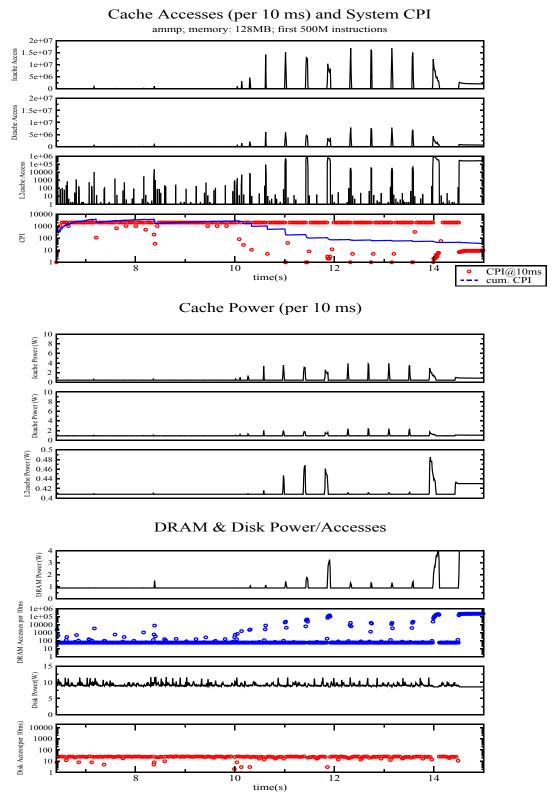

| Figure 6.3:  | I/O intensive phase of ammp                                         |     |

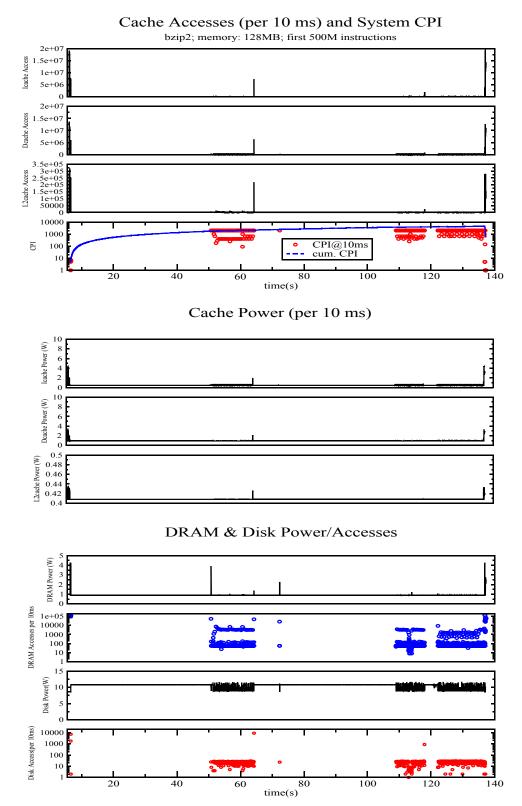

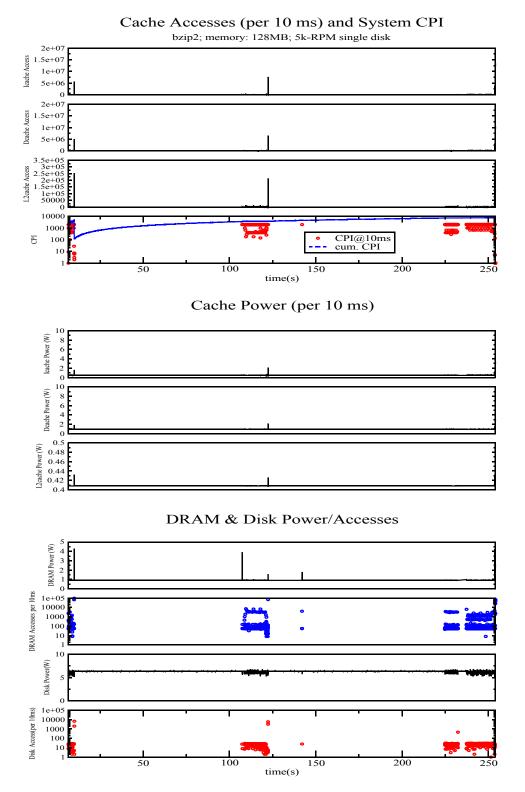

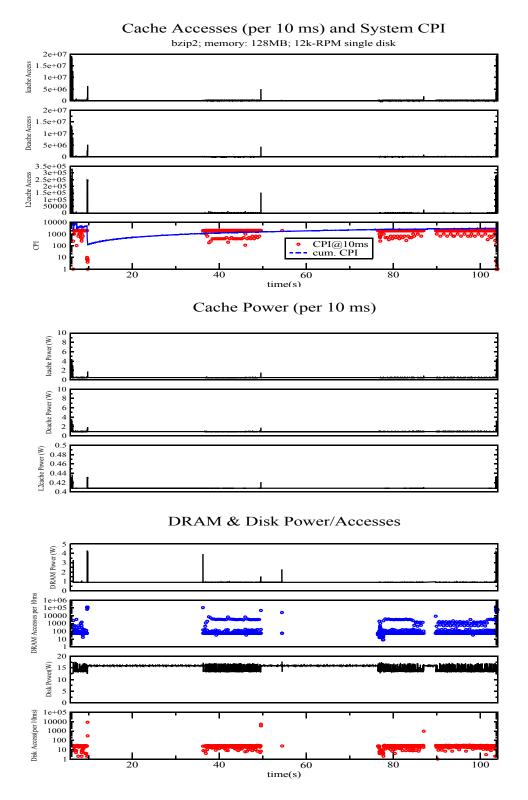

| Figure 6.4:  | I/O intensive phase of bzip2                                        |     |

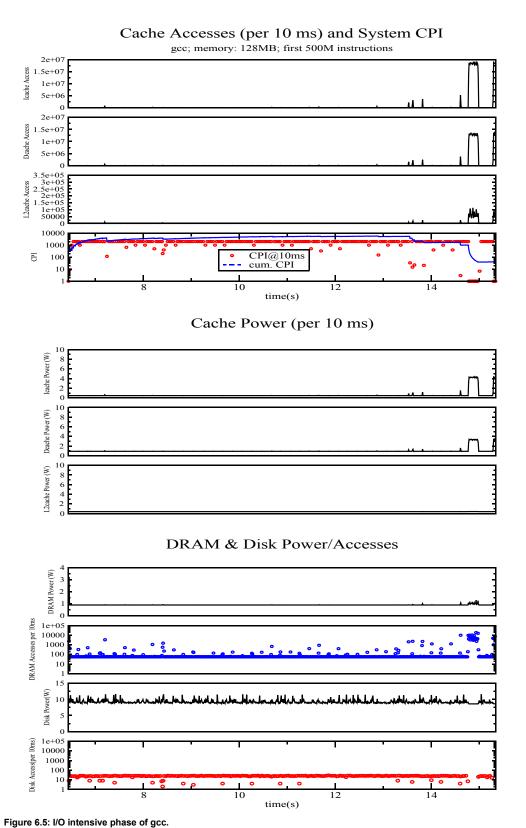

| Figure 6.5:  | I/O intensive phase of gcc                                          |     |

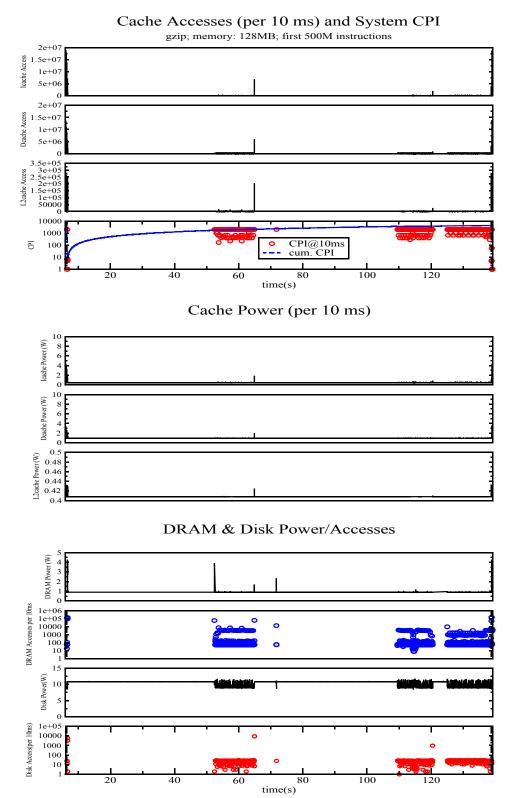

| Figure 6.6:  | I/O intensive phase of gzip                                         |     |

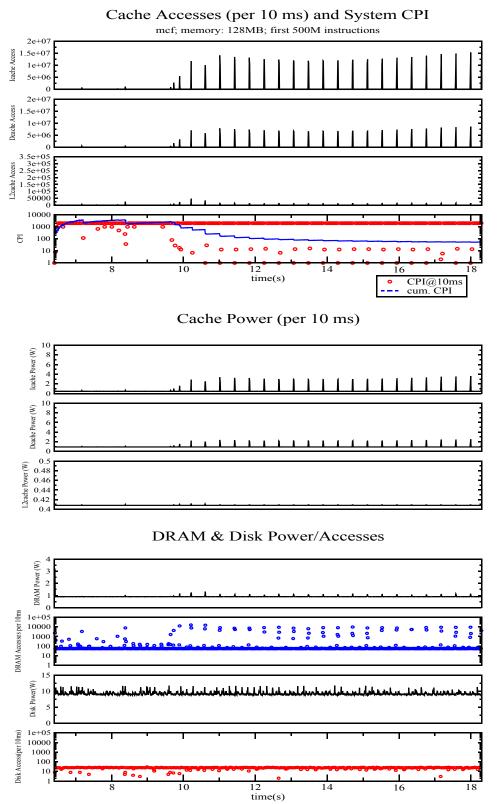

| Figure 6.7:  | I/O intensive phase of mcf                                          | 109 |

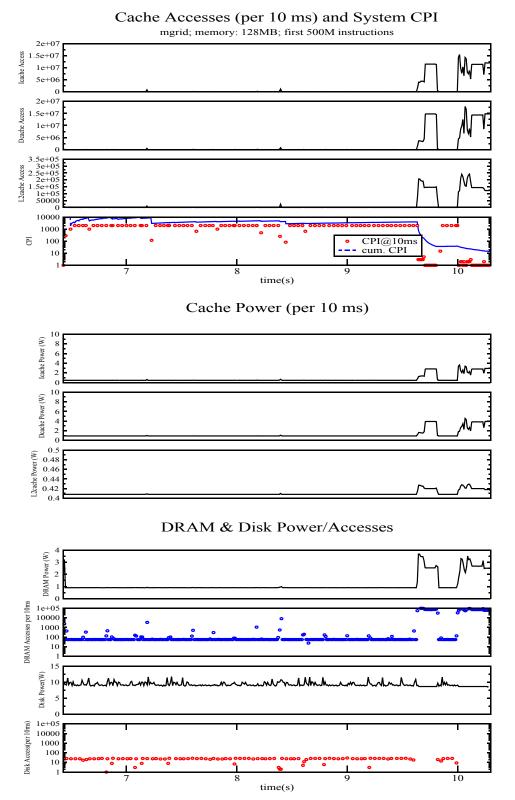

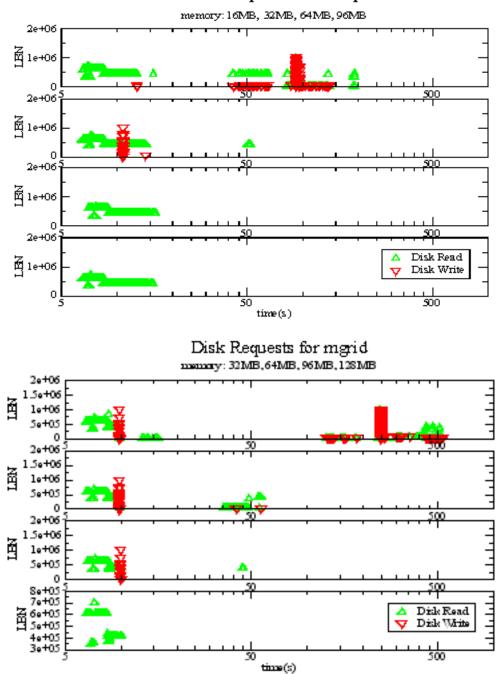

| Figure 6.8:  | I/O intensive phase of mgrid                                                                                                         | 170      |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------|----------|

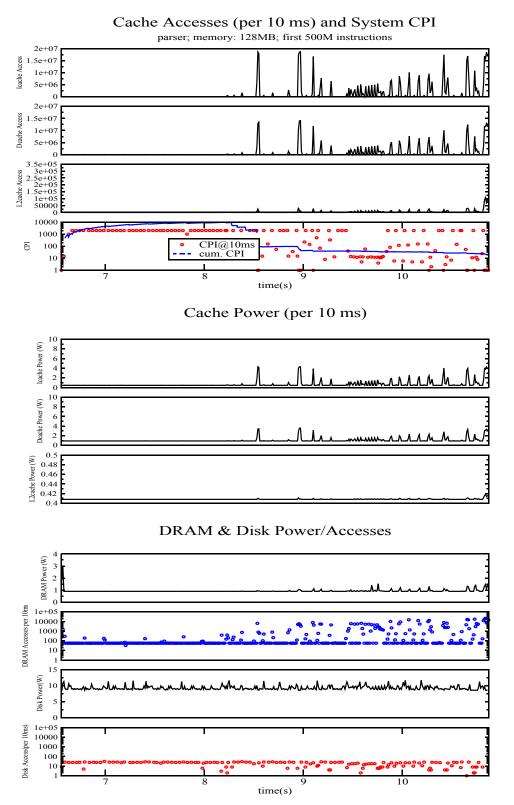

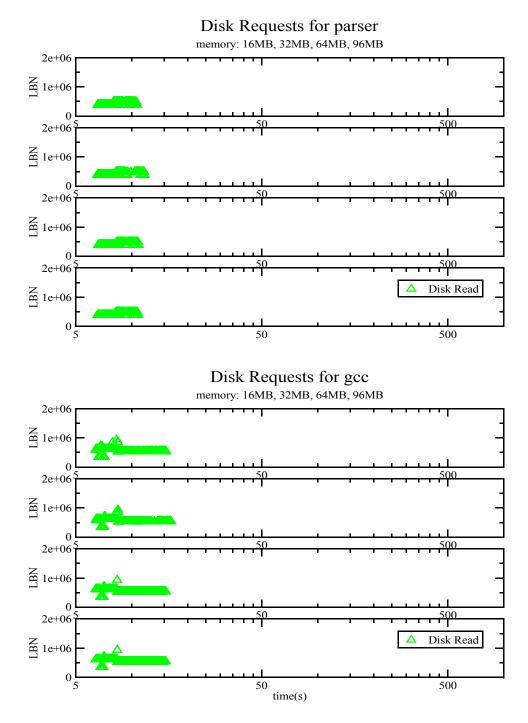

| Figure 6.9:  | I/O intensive phase of parser                                                                                                        | 171      |

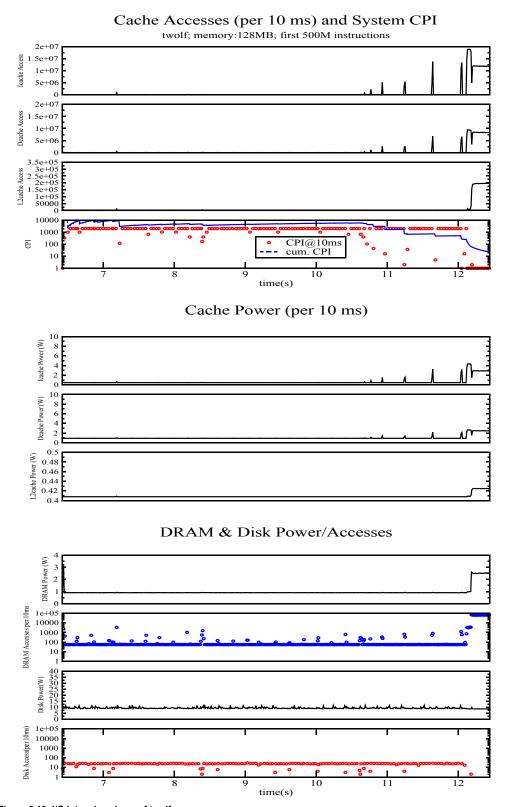

| Figure 6.10: | I/O intensive phase of twolf                                                                                                         | 172      |

| Figure 6.11: | I/O intensive phase of vortex                                                                                                        | 173      |

| Figure 6.12: | Memory Size Exploration.                                                                                                             | 176      |

| Figure 6.13: | ammp and mgrid Disk Activities                                                                                                       | 178      |

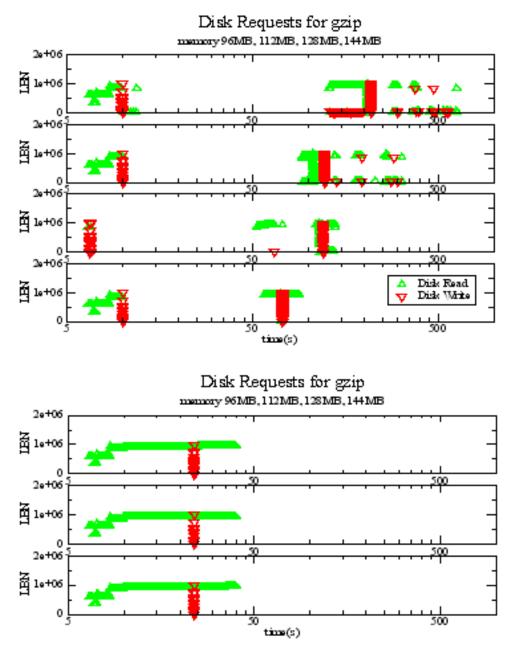

| Figure 6.14: | gzip Disk Activities                                                                                                                 | 179      |

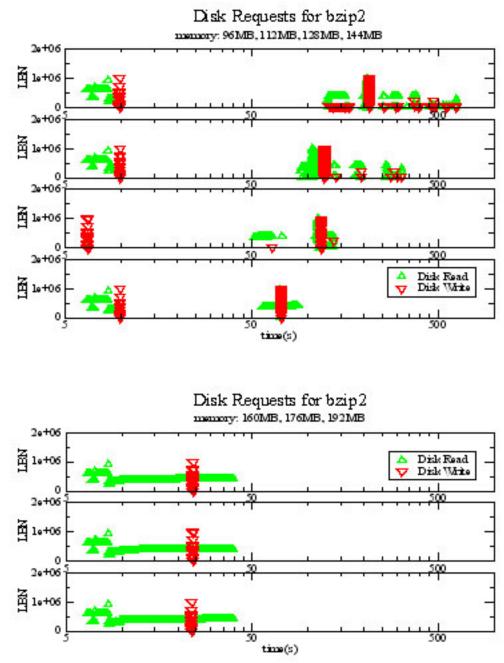

| Figure 6.15: | bzip2 Disk Activities                                                                                                                | 180      |

| Figure 6.16: | parser and gcc Disk Activities                                                                                                       | 181      |

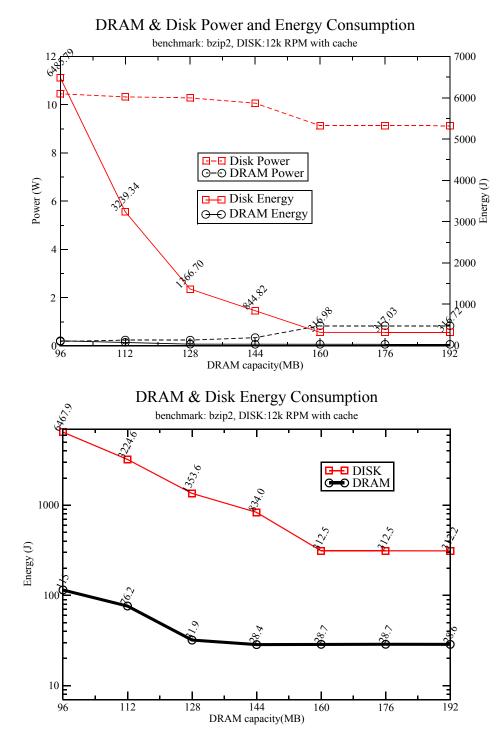

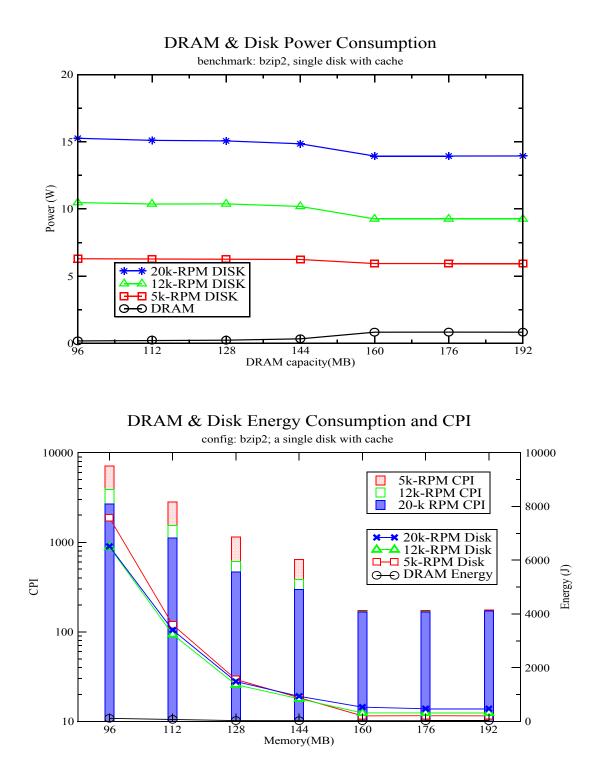

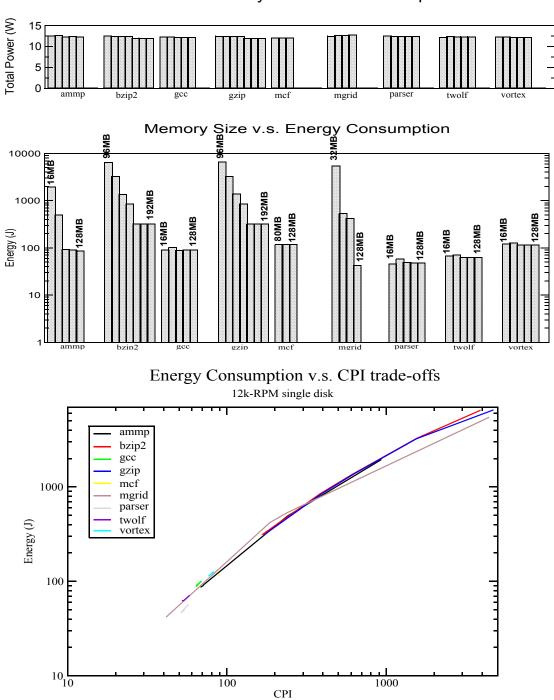

| Figure 6.17: | Power Dissipation and Energy Consumption of DRAM and a Disk                                                                          | 184      |

| Figure 6.18: | DRAM & Disk Power Dissipation and Energy Consumption                                                                                 | 185      |

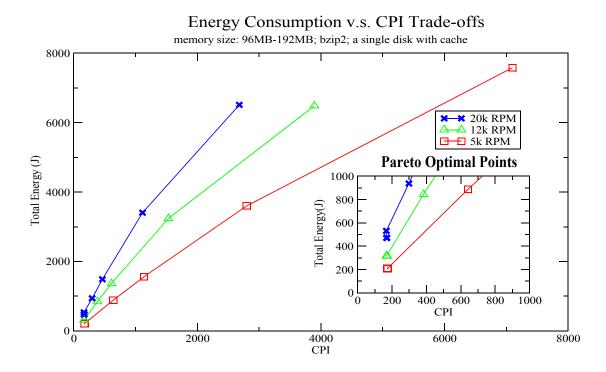

| Figure 6.19: | Energy Consumption v.s. CPI Trade-offs.                                                                                              | 186      |

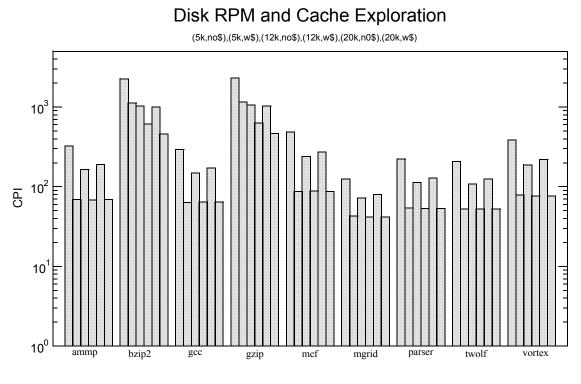

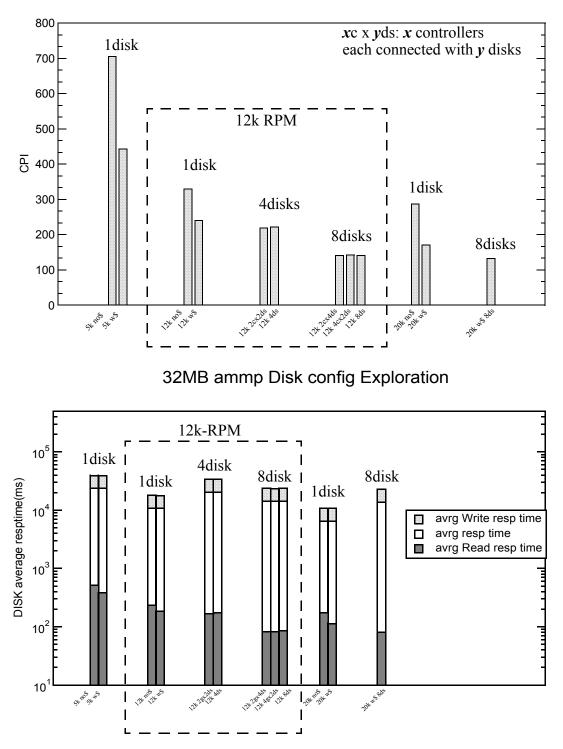

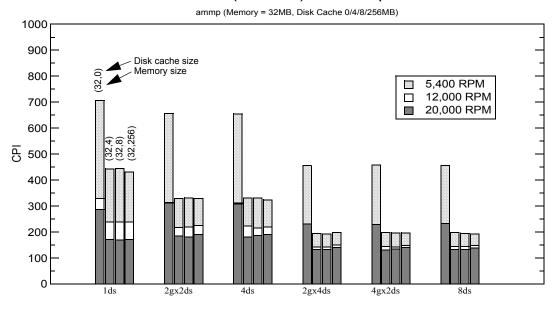

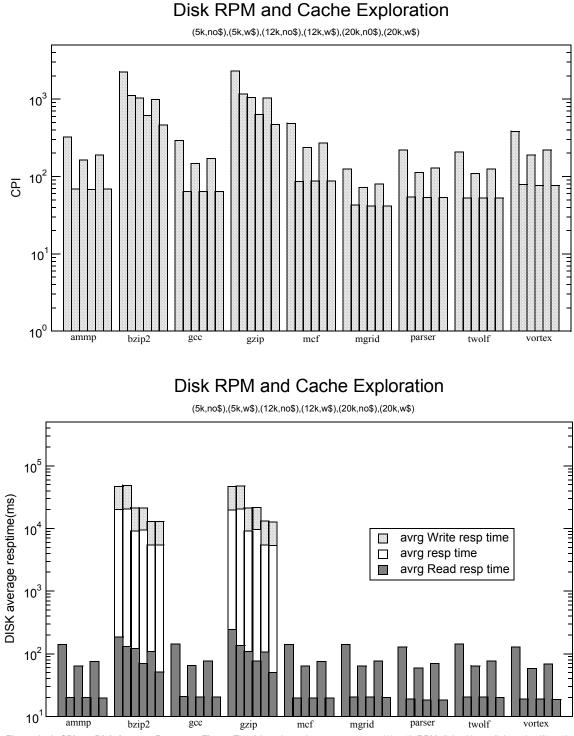

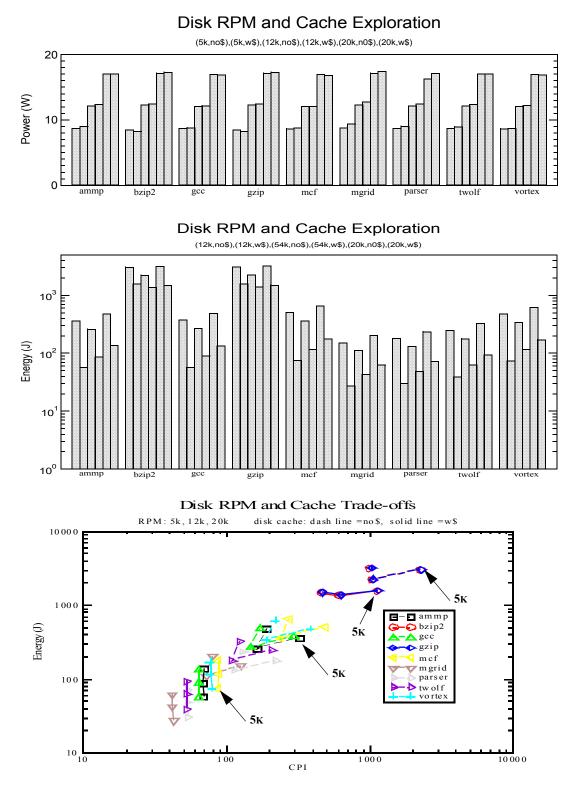

| Figure 6.20: | CPI due to the disk RPM and disk cache                                                                                               | 188      |

| Figure 6.21: | The interaction in the memory hierarchy for a system with a 5k-RPM drive                                                             |          |

| Figure 6.22: | The interaction in the memory hierarchy for a system with a 20k-RP drive                                                             |          |

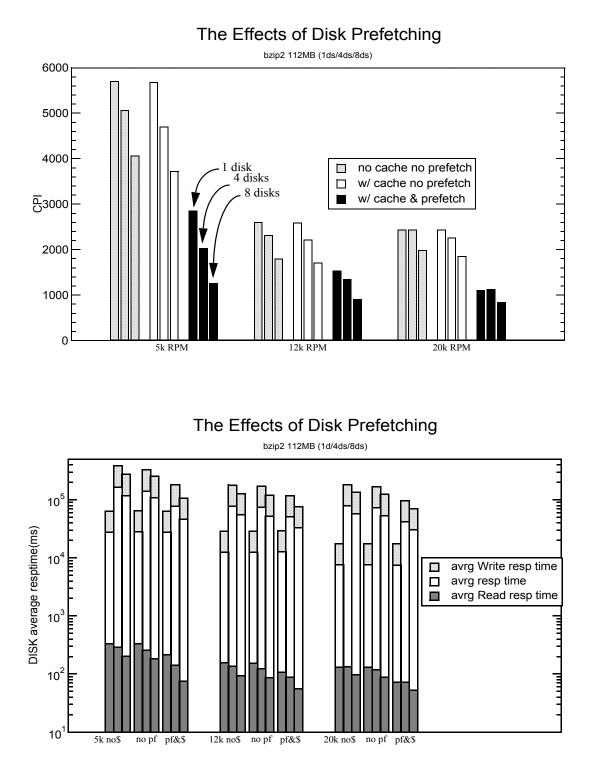

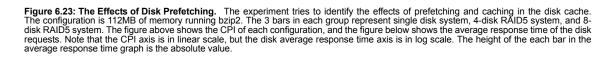

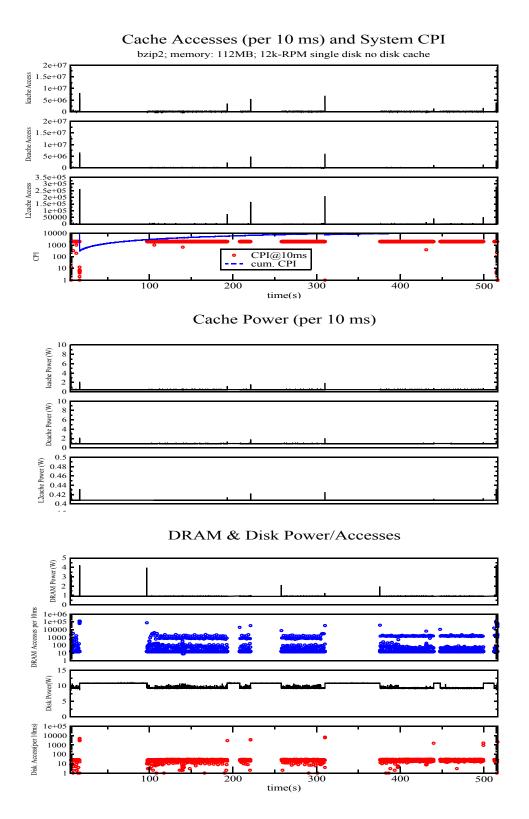

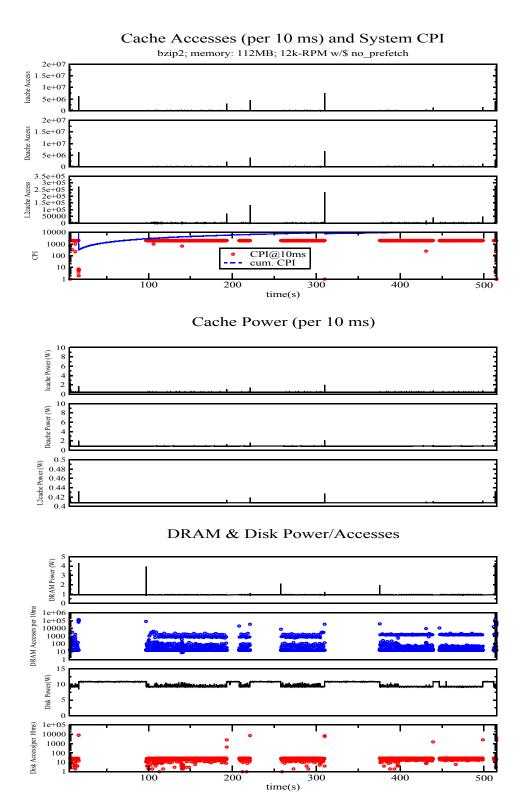

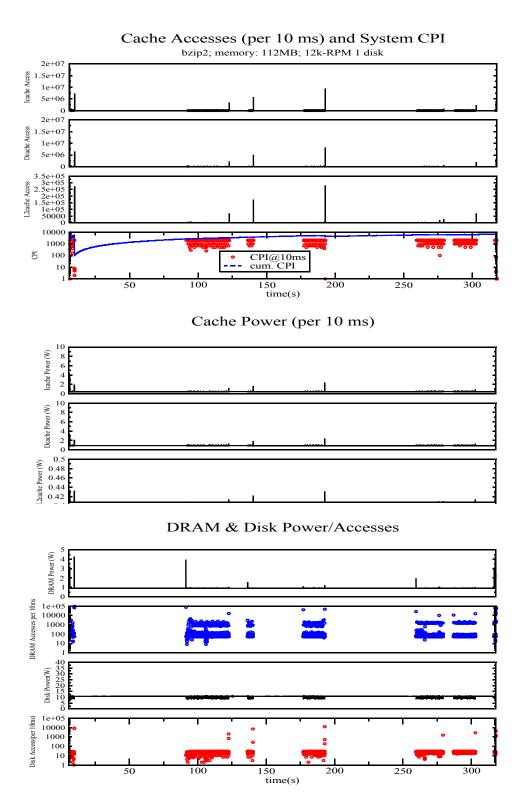

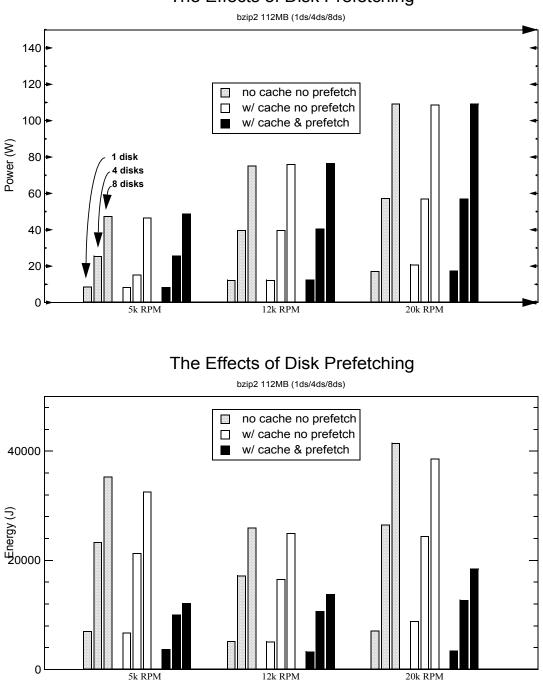

| Figure 6.23: | The Effects of Disk Prefetching                                                                                                      |          |

| Figure 6.24: | The interaction of the memory components in a system without disk                                                                    | cache    |

| Figure 6.25: | The interaction of the memory components in a system with disk can no prefetching                                                    | che but  |

| Figure 6.26: | The interaction of the memory components in a system with disk can and prefetching                                                   | ching    |

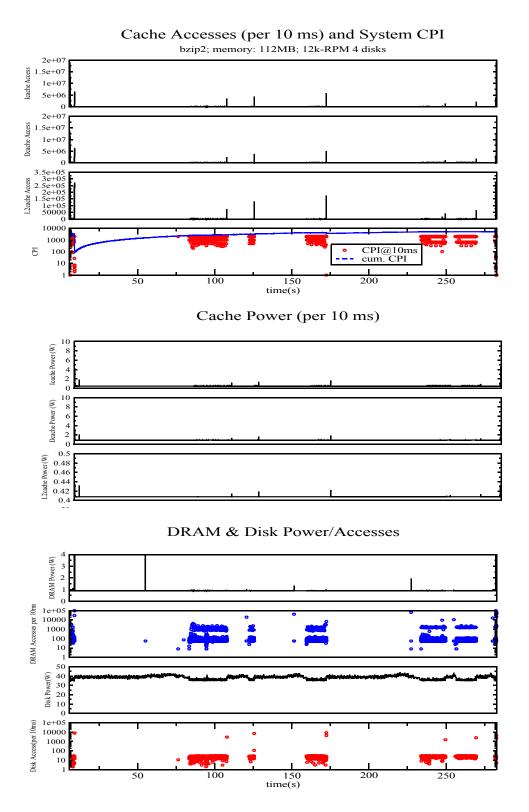

| Figure 6.27: | RAID5 configuration                                                                                                                  |          |

| Figure 6.28: | Disk RAID5 Configuration with different RPMs                                                                                         |          |

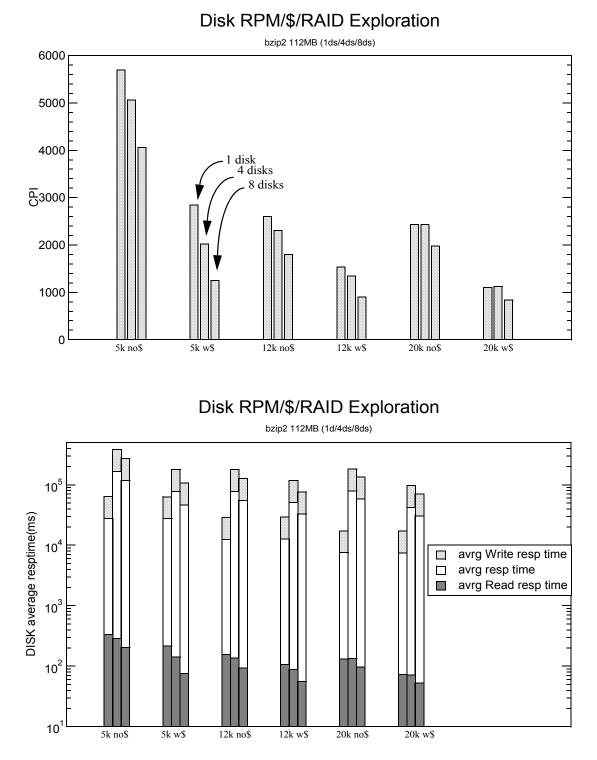

| Figure 6.29: | RAID5 with no writes                                                                                                                 |          |

| Figure 6.30: | The interaction between the memory components in the hierarchy of system with 4-disk RAID system                                     | fa       |

| Figure 6.31: | The interaction between the memory components in the hierarchy of system with 8-disk RAID system                                     | fa       |

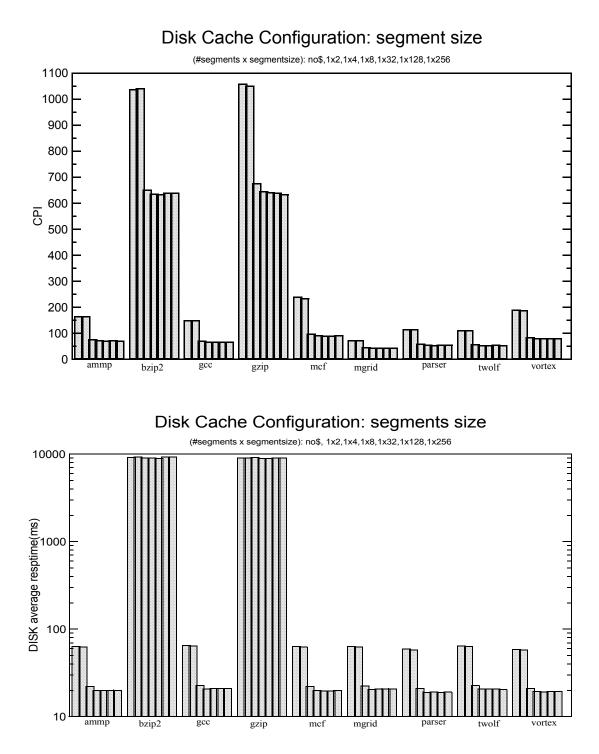

| Figure 6.32: | The Effects of Disk Cache Size by varying the Segment Size                                                                           |          |

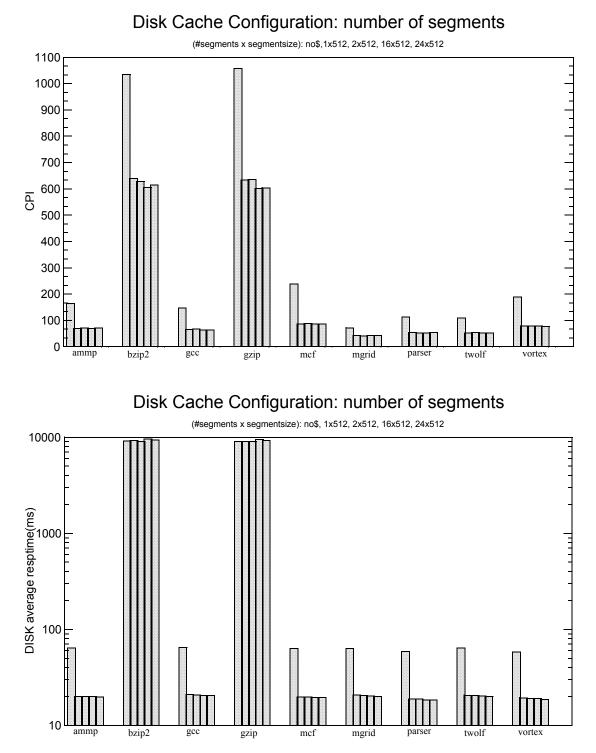

| Figure 6.33: | The Effects of Disk Cache Size by varying the Number of Segments                                                                     |          |

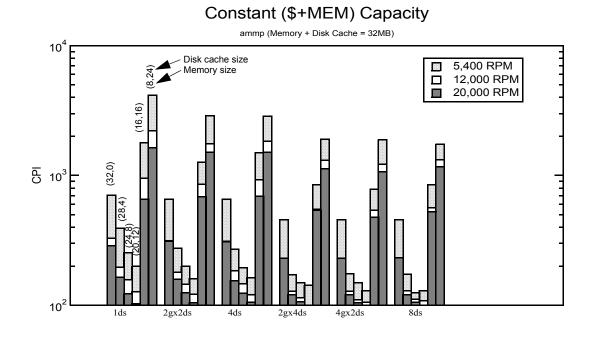

| Figure 6.34: | The Trade-offs between Memory Sizes and Disk Cache Sizes                                                                             |          |

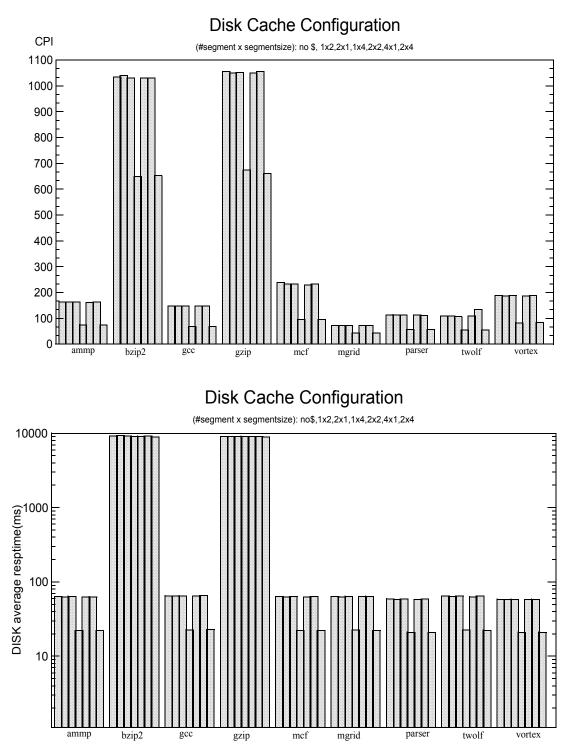

| Figure 6.35: | Disk Cache Organization                                                                                                              |          |

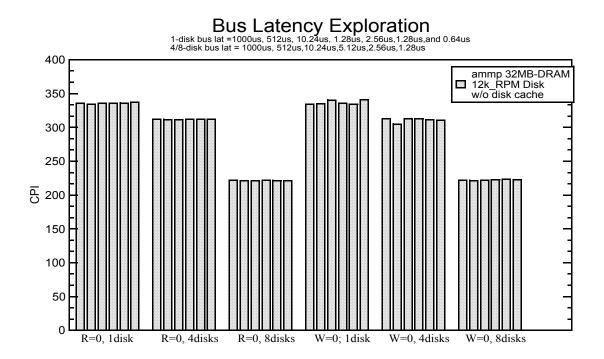

| Figure 6.36: | Bus Latency Exploration                                                                                                              |          |

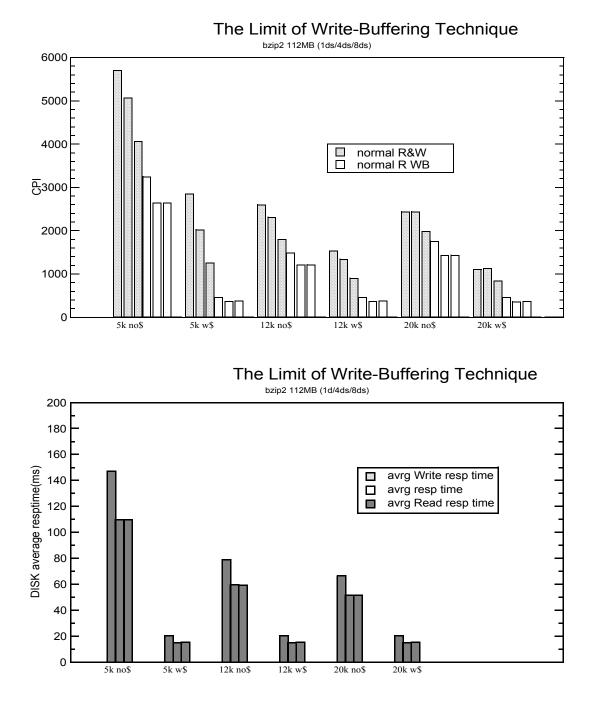

| Figure 6.37: | The Limit of Write-Buffering Technique                                                                                               |          |

| Figure 6.38: | The interaction of the memory components in the hierarchy in a sing system with perfect write buffering                              | gle disk |

| Figure 6.39: | The interaction of the memory components in the hierarchy in a syst<br>4-disk RAID disk subsystem along with perfect write buffering | em with  |

| Figure 6.40: | The interaction of the memory components in the hierarchy in a system with 8-disk RAID disk subsystem along with perfect write buffering |   |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------|---|

| Figure 6.41: | CPI v.s. Disk Average Response Time                                                                                                      |   |

| Figure 6.42: | System CPI Breakdown                                                                                                                     |   |

| Figure 6.43: | Power and Energy Consumption in the system with different memory size                                                                    |   |

| Figure 6.44: | Power and Energy Consumption for the system with different RPM and the presence of disk cache                                            |   |

| Figure 6.45: | Power and Energy Consumption of the system with Disk<br>Caching/Prefetching                                                              | 0 |

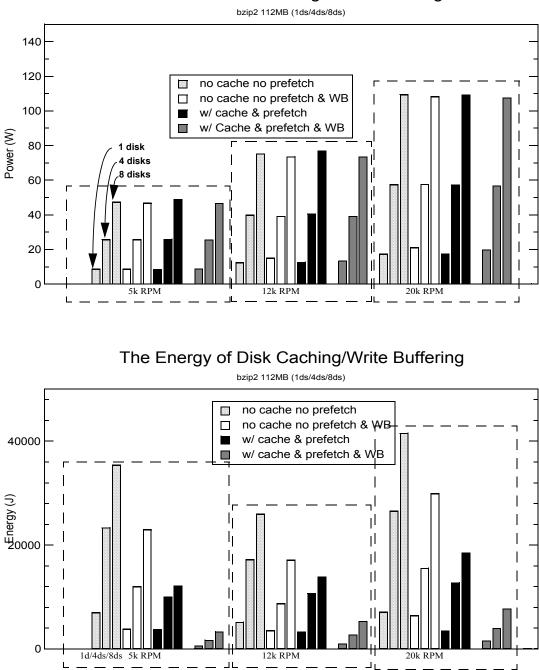

| Figure 6.46: | Power and Energy Consumption for Caching and Perfect Write Buffering                                                                     |   |

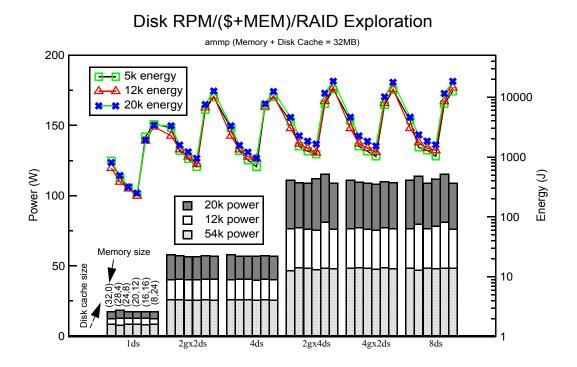

| Figure 6.47: | Power and Energy Consumption for the system with constant sum of memory size and disk cache                                              | 3 |

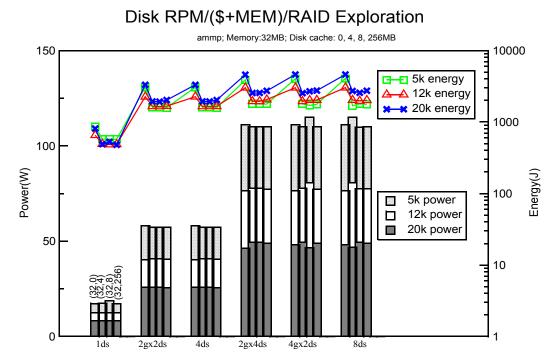

| Figure 6.48: | Power and Energy Consumption for the system with different size of disk cache                                                            | 4 |

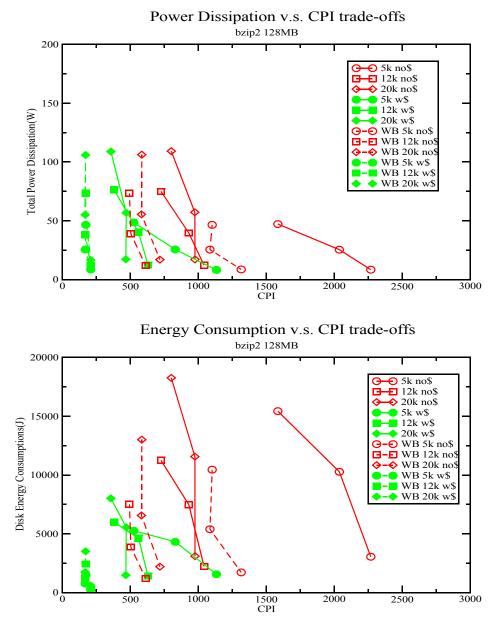

| Figure 6.49: | Power Dissipation/Energy Consumption v.s. CPI trade-offs                                                                                 | 5 |

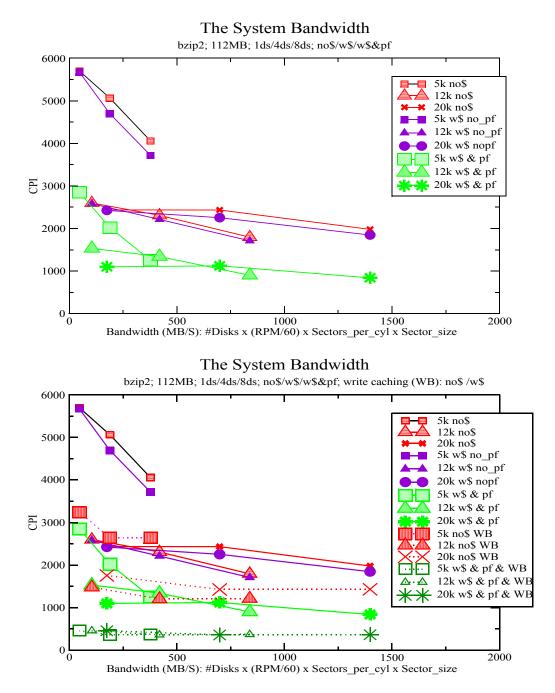

| Figure 6.50: | The System Bandwidth                                                                                                                     |   |

| Figure 6.51: | The interaction in memory hierarchy in our base configuration with 128ME of memory                                                       |   |

| Figure 6.52: | The interaction in memory hierarchy in a system with 512MB of memory                                                                     |   |

| Figure 6.53: | The interaction in memory hierarchy in a system with 128MB of memory and a disk drive with perfect write buffering                       |   |

| Figure 6.54: | The interaction in memory hierarchy in a system with the same configuration with RAID disk system                                        |   |

### **CHAPTER 1: INTRODUCTION**

#### **1.1. Problem Description**

The 90/10 rule states that 90% of the execution time is spent in 10% of the code. Most studies, therefore, focus on the computation phase which contains the most repeated number of instructions--i.e. the main loops, are executed, believing that it is the most important part in the entire course of execution. The argument for this is to make the most repeated case fast. However, this dissertation takes a different path. We are not looking at the duration that the most repeated instructions are executed; we are looking at the duration that the most time spent in the execution.

| Run #          | User (s) | Kernel (s) | I/O stall (s) | Total (s) |

|----------------|----------|------------|---------------|-----------|

| 1 (cold cache) | 93.11    | 15.06      | 600.83        | 709       |

| 2 (warm cache) | 92.7     | 16.3       | 397.00        | 506       |

| 3 (warm cache) | 92.8     | 14.3       | 425.90        | 533       |

| 4 (warm cache) | 93.3     | 14.3       | 460.40        | 568       |

| 5 (warm cache) | 93.6     | 14.3       | 441.10        | 549       |

Table 1.1: Execution Time Breakdown for System #1: 750MHz CPU with 96MB memory

|                |          | ·          |               |           |

|----------------|----------|------------|---------------|-----------|

| Run #          | User (s) | Kernel (s) | I/O stall (s) | Total (s) |

| 1 (cold cache) | 90.4     | 6.4        | 164.20        | 261       |

| 2 (warm cache) | 90.1     | 6          | 126.90        | 223       |

| 3 (warm cache) | 89.8     | 5.7        | 129.50        | 225       |

| 4 (warm cache) | 90.5     | 5.5        | 121.00        | 217       |

| 5 (warm cache) | 90.3     | 6.1        | 168.60        | 265       |

|                |          |            |               |           |

Table 1.1 shows the execution time breakdown for gzip in a real system. The system has a 750MHz CPU with 96MB of the system memory and runs Fedora Core 3. Table 1.2 shows the execution time breakdown for gzip in another real system. The second system is the same system as the first system, but the system memory is set to 128MB. One would expect that the memory in both systems should be large enough to run a SPEC benchmark Though the systems spent significant amount of time executing the user code, they also spent more time stalling for I/O.

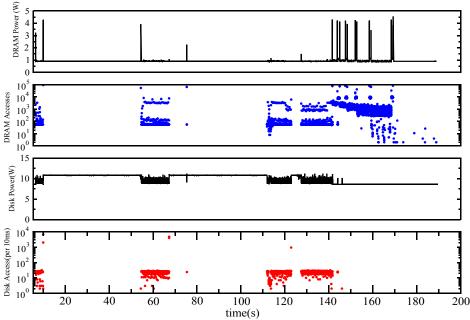

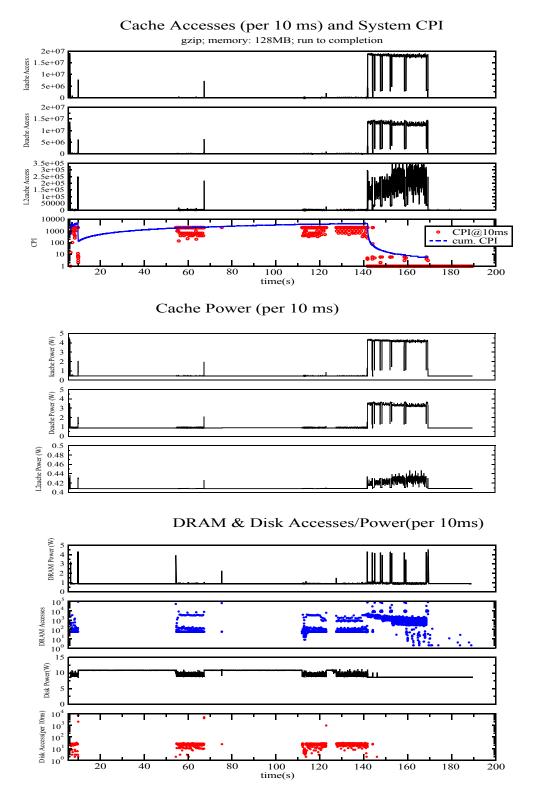

Figure 1.1 shows the simulation results of an entire execution of gzip, a spec benchmark, on our complete-system simulator--SYSim, in a single-processing environment. The system configuration used in this example is a 2-GHz Pentium processor, 128MB of main memory, and a 12k-RPM disk drive with built-in disk cache. The figure shows the interaction between all components of the entire memory hierarchy, including the level-1 instruction cache, the level-1 data cache, the level-2 unified cache, the DRAM, and the disk drive. All graphs use the same x-axis, which represents the execution time in seconds. The x-axis does not start at zero since the system boot time is excluded. Each data point is collected for every 10 milliseconds epoch. The CPI graph shows 2 system CPI values: one is the average CPI for any 10 milliseconds epoch, the other is the accumulated average CPI. The duration with no data point displaying means no instructions are executed due to the I/O latency. The application is run in single-user mode to make accurate calculation of execution time. Otherwise, the kernel would swap to other processes on a system call to read from disk. Therefore, disk delay shows up as stall time. The course of execution when the accumulated average CPI is over 100 is the I/O intensive phase (i.e. before the 140th second), while the

Figure 1.1: The System CPI. The figure shows the System CPI over the entire run of gzip. The system configuration is a 2-GHz processor with 128MB of memory and a 12k-RPM disk. The CPI graph shows 2 CPI values: one is the instant CPI for every 10ms, another is the accumulated average CPI. The duration having no data point means no instructions are executed due to the I/O latency. The course of execution when the accumulated CPI is over 100 is the I/O intensive phase, and the course of execution when the CPI is below 100 is the computation phase.

course of execution when the CPI is below 100 is the computation phase. Note that the CPI, the DRAM accesses, and the Disk accesses are in log scale.

During the course of the execution, there are I/O intensive phase and steady or main computation phase. The figure shows that the program spent a significant amount of the time, if not most, in the I/O intensive phase due to the I/O activities. Unlike the disk, the other components in the memory hierarchy cause very little activity during the I/O intensive phase. On the other hand, those components are accessed regularly during the computation phase which is where the most instructions are executed, and a phase during which the disk is mostly idle. Therefore, the I/O intensive phase has been exposed as a significant component due to the I/O latency with respect to the total execution time.

Most studies skip the I/O intensive phase due to the claim that it is unimportant as it is only executed once. However, despite being run only once, the I/O intensive phase takes far longer than other phases. The underlying reason for the lack of attention to this issue is that the I/O intensive phase is dealing with I/O activities which only a small number of tools implement due to the complexity and time-consuming experimentation. These tools can take years to develop, and a single data point on an experiment can take weeks or even months to execute. For these reasons, most publications conduct an experiment only on the computation phase and claim a single digit CPI value. Unfortunately, they entirely ignore the effects of the I/O intensive phase. As figure 1.1 shows, the CPI value can vary by many orders of magnitude due to the I/O activities during the long I/O intensive phase. CPI finally reduces to a single-digit number during the computation phase as portrayed by many studies. Therefore, the techniques that simply ignore the I/O intensive phase and claim 10% or even a factor of 2 improvement over only computation phase, as exhibited in most processor, cache, and DRAM enhancements, may have only minor impact for the entire course of execution.

The solution to this problem is to investigate the I/O. To obtain a system with more balanced phases, we require more understanding of the effects of the parameter configurations of the I/O to the entire system, especially during the I/O intensive phase. A variety of disk optimization techniques including caching, write buffering, prefetching, and parallel I/O have been invented to optimize I/O operations. These techniques have been in place in the server-classed disk drives for over 10 years. As the technology is getting cheaper with the time, there is a shift to using these techniques in PC disk drives as well. For example, in general, an optimizing technique would be first introduced in server drives. Then, a few years later, the technique will be implemented in desktop drives. As a result, an optimization technique would take approximately 10 years to shift from server class disks to mobile drives. In addition, with better technology, the disk physical characteristics are also improved, including the RPM (rotational speed in term of round-per-minute), the seek time, and the disk drive interface.

The effectiveness of these techniques in term of total system performance, however, is not clear because they have been studied in isolation by different researchers using different methodologies. As the performance gap between the processor and disk-based storage continues to widen, increasingly aggressive optimization of the storage system is needed. This requires a good understanding of the real potential of the various I/O optimization techniques and how they work together. Therefore, we are required to study the effects in the full-system scale.

To our knowledge, this dissertation is the first to explore disk design space during the I/O intensive phase, and the results are reported in both total system performance and the power/energy consumption. We will show later that the overall system performance can be improved greatly by the enhancements in the disk drives, i.e. using disk caching and prefetching can improve the performance by the factor of 2, and write-buffering techniques can improve the performance by the factor of 10. Moreover, the combination of disk caching/prefetching and the write-buffering technique is the most important enhancement to focus on since the enhancement can improve the total system performance over an order of magnitude without increasing the energy consumption significantly. Increasing the disk RPM and the number of disks in RAID disk system also have an impressive improvement over the total system performance. However, since such techniques can consume significant energy, they have trade-off to be considered carefully. Our studies also revealed that as the capacity of the main memory decreases to the capacity which causes memory page swapping during the I/O intensive phase, the overall system performance decreases greatly. This type of behavior will also continue to show as the size of application's memory footprint grows, which is the trend for the future applications. Therefore, increasing the memory size will only solve the problem in the short term. The long-term solution is to improve the disk system performance.

Recently, the design trade-off of performance versus power consumption has received much attention because of the following [36]:

- 1. the ever-growing number of disk-based mobile systems that need to provide services with the energy supplied by a battery of limited weight and size;

- 2. the technical feasibility of high performance computation due to heat extraction; and

concerns about the operating costs of large systems caused by electric power consumption as well as the dependency of systems operating at high temperatures because of power dissipation. For example, a data warehouse of an Internet service provider with 8000 servers requires 2 MW [36].

Thus, the demand for low-power systems is increasing not only for mobile systems but also for general-purpose systems. Additionally, the energy consumption of the computer systems will scale up as they become more complex.

In general, optimization techniques aiming at performance do not necessarily optimize power consumption and can often lead to more power consumed. An et al. [33] demonstrate this fact with spatial database application. They evaluate three spatial indexing methods for memory resident database in embedded systems from both the energy and performance angles. Their experimental results show that one indexing method is superior to others in performance angle while aggravating the power dissipation. Other publications also exhibit that performance optimization techniques can aggravate the power dissipation. For example, in [34], the simulation results of an embedded system running an MPEG video show that using a 4-way set-associative, burst SDRAM L2 cache in addition to the L1 cache improves performance by approximately 10% but almost doubles the total energy consumption. Therefore, since there are trade-offs in the performance and energy consumption, care must be taken to apply the performance optimizations.

Energy-efficient design requires reducing power dissipation in all parts of the design. Design decisions in a part of a system (e.g., the micro-architecture of a computing element) can affect the energy consumption in another part (e.g., memory and/or memory-processor busses), or even affect the energy consumption in many parts. For example, reducing miss rates in L1 cache can reduce the access and power consumption in other lower-level memory. Another example is that a power reduction technique in the memory can be responsible for increasing the power consumption in the processor as demonstrated by Kandemir et al. [40]. They evaluate five state-of-the-art high-level compiler optimizations on energy consumption, considering both the processor core (datapath) and memory system. They found that, while most performance oriented optimizations reduce the overall energy consumption, they also increase the energy consumption in the datapath. As a result, energy-efficient system-level design must address the reduction and balance of power consumption in all constituents.

Nowadays, the cost per memory bit is extremely low, and sheer memory size is rarely the main issue in system design. In stead, memory performance and power are now the key challenges. Memory accesses become slower with respect to the processor and consume more power with increasing memory size. Many studies show that memory power and access time dominate over 50% of the total power and performance for computations with large storage requirements[37, 38, 1]. As a result, memory becomes the main bottleneck.

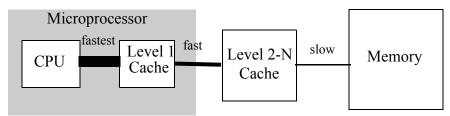

All advanced memory organizations rely on the concept of memory hierarchy. High hierarchy levels are made of small memories, close to computation units, and tightly coupled with them. Low hierarchy levels are made of increasingly large memories, far from computation units, and shared. Hierarchical organizations reduce memory power by exploiting non-uniformities in access frequencies. Most applications access a relatively small area in memory with high frequency, while most memory locations are accessed a small number of times. In a hierarchical memory, frequently-accessed locations should be placed in high hierarchy levels, closer to the processor, thereby minimizing average cost per access.

One technique which is implemented in many levels of memory hierarchy is caching. Caching temporarily holds data that is likely to be utilized in a faster memory, called cache. The term "cache" is used in every level in the memory hierarchy where the technique is applied. Therefore, terms, such as Memory Cache, Disk Cache, and File System Cache, confuse most people, even the people in Operating Systems and disk research. Sometimes they use these terms interchangeably. To clarify the terms used in this dissertation, the terms are defined as following. All Memory Cache, Disk Cache, and File System Cache serve the same purpose, which is to hide the disk latency by caching the data in the location closer to the processor. In this dissertation, Memory Cache indicates the level-1 data cache, level-1 instruction cache, level-2 cache, and so on. Disk Cache, sometimes called Disk Buffer, is a set of memory chips physically located in a disk drive. Disk Cache usually exists without the knowledge of the operating system, and it is controlled by the processing unit embedded in the disk drive. The File System Cache is a part of the system memory, managed by the operating system and reserved for files which are read from the disk system. Therefore, the File System Cache is physically located in the main memory which is usually in the DRAM, but it can be anywhere in the memory hierarchy.

Approaches to memory optimization considering both power and performance in the literature can be grouped into three classes [36]:

Memory hierarchy design assumes a given dynamic trace of memory access, obtained by profiling an application, and produces a customized memory hierarchy. Many publications present strategies for the optimal cache configuration [43, 44, 45, 46, 47], and others partition each memory level into subbanks to be able to put into low-power mode when not used [47, 49, 50, 51]. Many recent publications insert specialized buffers in the hierarchy [52, 53, 54, 55, 56, 57] to improve data locality in each memory level and/or to reduce traffic between them. These specialized buffers are also used as instruction compression buffers [58, 59, 60, 60].

- 2. Computation transformations for memory optimization assumes a fixed memory hierarchy and tries to modify the storage requirements and access patterns of the target computation to optimally match the given hierarchy. For example, data structure selection [63, 64], register and memory allocation [65, 66], dynamically switching devices to low-power mode [67, 68], extending the low-power duration of a device by code transformation [69, 70], and reducing memory address bus transitions [71, 72, 73, 74].

- 3. *Synergic memory and computation optimization* tries to concurrently optimize memory access patterns and memory architecture [41, 42, 62].

In this dissertation, we explore the disk drive optimization techniques, which are physical improvements and enhancements with additional hardware. Since we only concentrate on customizing a level in memory hierarchy without attempts to modify the access pattern, our approach can be classified into the first group, *Memory hierarchy design*.

A magnetic disk has been considered a fundamental component in a computer system since 1965 [39]. It primarily serves as long-term, non-volatile storage for files, and as a level of the memory hierarchy below main memory. Disk is included in the virtual memory

implemented in most popular operating systems as a slow memory during program execution. Though disk is an indispensable part of general-purpose computer systems, so far no literature addresses the complete picture of the memory hierarchy including disk, or how memory systems (caches and DRAM) interact with disk in both performance and power dissipation. As we will show in the next section, one reason is that there are no proper tools available in the public domain for such studies. Such a tool would have to demonstrate accurate interactions between the caches, the main memory, and the disk via I/O requests from the operating system. The components must be implemented in detail to capture the systemic interactions between them. Furthermore, as low-power consumption is another system requirement, the tool needs to estimate the instantaneous power dissipation in each component to reflect the efficiency in power consumption. Such tools are considered very complex to implement.

Therefore, SYSim was created to be a complete-system simulator aiming at complete memory hierarchy studies. SYSim focuses on demonstrating the detailed interaction in memory hierarchy in both performance and power domains. In this dissertation, we employed SYSim to explore several disk enhancements and the disk physical technology improvements during the I/O intensive phase. The experimental results were reported in both total system performance domain and the power/energy consumption domain.

#### **1.2.** Contribution and Significance

The contribution in this dissertation is two-fold. First, we explore several disk enhancements and disk physical technology improvements in both isolation and in combination, considering both total system performance and the power/energy consumption, focusing on the I/O intensive phase. Secondly, we create a complete-system simulator, SYSim, to demonstrate the detailed interaction in memory hierarchy in both performance and power domains.

With SYSim, we are able to conduct the complete-system experiments to evaluate the disk optimization techniques effect on actual total system performance and power/energy consumption. To our knowledge, this dissertation is the first to explore several disk enhancements and technology improvements both in isolation and in combination during the I/O intensive phase of applications. The disk enhancements we studied include disk caching, prefetching, write buffering, and parallel I/O. In addition, the disk technology improvements we explored include the disk seek time, rotational speed, and interface data rate. The results are reported in terms of both total system performance and the power/energy consumption. We captured the following intriguing behaviors:

- During the I/O intensive phase which consists of both disk reads and writes, average CPI tracks only average disk read response time not overall average disk response time, which includes both disk read/write response time. This is important because most disk studies report performance in terms of average disk response time.

- The effect of the size of the disk cache is limited to the presence of the cache with a particular size. That is increasing the size of the disk cache will not result in better performance if the disk cache is already large enough. This behavior is also agreed

with the file system cache size and disk cache size exploration by Zhu and Hu in [75].

- In the disk read-dominating benchmarks, Disk Prefetching is more important than increasing the disk RPM. That is rotational latency and bandwidth can be overcome by simple prefetching during disk read phase.

- In the benchmarks containing both disk reads and writes, the disk RPM matters. This is because the disk maintains the concepts of non-volatile storage, so disk write requests must be processed to the disk immediately. The experiment shows that using some techniques, such as, NVRAM to buffer the writes, may improve the performance significantly.

- Increasing the number of disks in a RAID system does not proportionally translate into better performance. For instance, increase number of disks form one to eight does not improve performance by the factor of 8. Worse, the power/energy consumption does increases proportionally by the number of disks: a system with 8 disks dissipates roughly 8 times the power of a single-disk system.

- The cost of writing in RAID system is significant as the RAID systems usually suffer from small writes [80]. If the cost of a write is reduced, such as by implementing write buffer mechanism, the overall system performance will be improved significantly.

- Individual DRAM chips dissipate little power, but a system must have a substantial amount of DRAM to keep the disk from dissipating significant power. Moreover, when there is sufficient DRAM capacity in the system, the total DRAM power can be significant.

- The energy consumption seems to have more significance than the power dissipation. The energy consumed can grow significantly with different disk parameters because the I/O latency substantially prolongs the program execution time.

- In the systems with fast disks, increasing the system bandwidth alone fails to improve performance directly. To significantly improve total system performance further, disk enhancement techniques are required.

### 1.3. Organization of Dissertation

The dissertation is organized as follows: Chapter 2 provides an overview of the memory hierarchy. Both Caches and DRAM-based memory systems from the system level down to the circuit level are discussed to provide the reader fundamental insights about the memory hierarchy. Chapter3 gives a background about disk drives in computer systems, and describes a drive's physical components, data organization, and interfaces. Chapter 4 discusses related works in the literature for the dissertation. It consists of insight about system simulators in the research community, disk drive enhancements, and disk drive technology improvement that we considered in this dissertation. Methodology for proposing simulator, SYSim, is discussed in Chapter 5. It details the parameter settings in our experiments, the simulator implementation details, and sample output to provide more insight in our proposed complete-system simulator. Chapter 6 presents the experiments and results for the memory system studies, mainly about system-level behaviors focusing on the disk system configuration. Finally, we end the dissertation with the conclusions.

### **CHAPTER 2: MEMORY HIERARCHY**

In this chapter, we will be providing background information regarding the memory hierarchy in a general-purpose computer system, primarily focusing on the cache and main memory. The chapter will consist of detailing the memory hierarchy in general. Other topics discussed will be the first level in the memory hierarchy and cache. A detailed background on cache design is given to serve as the foundation while discussing concepts used in cache tools. We also include the basics of cache design. The cache tools we used in our experiment, CACTI and Wattch, are also introduced, as well as a general explanation of how the selections have been made for the cache configuration and power dissipation calculation. After that, we discuss the main memory included in a general-purpose computer, based on DRAM (Dynamic Random Access Memory). Then, the basic structures of DRAM devices and memory system organizations are described in some detail. The section starts with the description of the smallest unit of the DRAM, a memory cell, moves upward to the DRAM device, and then to DRAM system organization. Next, the DRAM memory access protocol is discussed to provide an explanation of fundamental DRAM operations and interactions between them. Finally, the chapter concludes with abstracted concepts of DRAM memory controller design.

#### 2.1. Memory Hierarchy

Figure 2.1: Memory Hierarchy in Typical Computer Systems.

A relatively unlimited amount of fast memory with low cost is always a requirement for future computer systems. Memory hierarchies have been invented to support this requirement. A memory hierarchy is defined as the hierarchical arrangement of storage in computer architecture. The hierarchy takes into consideration the advantage of both locality of accesses and the cost-performance ratio of memory technologies. The principle of locality states that most programs do not access all code or data in well-distributed spatial or temporal distributions. The programs have some forms of locality in their accesses. Another principle is the memory hierarchy organization. Each level of the hierarchy is organized in such a way that it can be accessed with higher speed and lower latency than lower levels. These two principles are the basis of the hierarchy, which is based on memories of different speeds and sizes. Since fast memory technology is expensive, a memory hierarchy organizes different speeds and sizes of memory into several levels, with the smaller, faster, and more expensive memory placed closer to the processor. The goal is to provide a memory system with cost comparable to the cheapest level of memory and speed comparable to the fastest level of memory. The levels of the hierarchy usually are inclusive, meaning that data located in the upper levels are also included in the levels below. The data in the memory hierarchy may also be exclusive, which means data is allocated in only one level at a time among multi-level caches. Note that each level maps addresses from a larger memory to a smaller but faster memory that is placed closer to the processor in the hierarchy. As part of address mapping, the memory hierarchy also provides address checking and protection schemes preventing harmful address accesses.

### 2.2. Virtual Memory

Virtual memory allows programs to run in a memory address space whose size and addressing are independent from the computer's physical memory. If a program exceeds the physical memory capacity, virtual memory automatically loads or unloads pages without the user program knowing. A page is simply a chunk of memory that is loaded or unloaded as a single unit. Therefore, virtual memory reduces the startup time for a program since only the necessary pages are loaded at startup. On the other hand, in a multiprocessing environment, multiple processes can run simultaneously with their own independent address spaces. Virtual memory divides physical memory into pages and allocates them among different processes. It locates the unnecessary pages in some secondary storage and loads only pages necessary for multiple processes at a given moment. It automatically manages the two levels of the memory hierarchy, which are main memory and secondary storage. Virtual memory also protects the processes' address spaces by restricting the processes to only the address spaces to which they belong.

With virtual memory, the address referenced by the processor is called a virtual address. The virtual addresses are translated by a combination of hardware and software to physical addresses, which are used to access main memory. This process is called memory mapping or address translation. A data structure called a page table is used in address translation. Each page table entry is indexed by the virtual page number and contains the physical page address. Two virtual page numbers can map to the same physical page frame. However, the size of the page table is quite large compared with the size of the system memory: the page table can occupy approximately 0.1 -1% of the system memory. Additionally, the address translation process would deteriorate the system performance if every memory access required another access for address translation.

The TLB (translation look-aside buffer) is introduced to mitigate the cost of the address translation process. Since the address translations for accesses have spatial locality, the TLB is used to improve address translation by caching recently accessed page table entries. The process of address translation via TLB can be placed before or after the cache depending on what scheme is used. Therefore, address translation is directly related to caching, and it will be discussed further in the next section regarding cache operations. The page table entries cached by TLB have been recently referred to by the processor and therefore their physical pages are located in main memory. When the processor refers to an address, the system looks it up in TLB first. If the entry is found in the TLB, the referring virtual address is translated to a physical address accordingly. This process eliminates the need to look up the address in the actual page table located in main memory. Therefore, accessing memory to look up a page table entry for address translation is not necessary in this case. However, when a TLB miss occurs, which is when the referring page table entry is not found in the TLB, the system unavoidably accesses the page table for the entry. The TLB misses may cause a series of activities to allocate a new page for the entry, including memory page allocation, page table entry creation, and TLB entry insertion, depending on the status of the page.

The TLB miss is handled by the operating system or hardware. If the memory page was previously allocated, the operating system would only require looking up of the page table entry in the page table and inserting it into the TLB. Then the access can be restarted. In the process of scanning through the page table, the operating system may find that the referring entry is actually *unmapped*. A *mapped* virtual page is defined as a virtual page previously allocated by the operating system, and whose mapping information is currently maintained under the operating system's awareness. In contrast, an *unmapped* page can occur in two situations which are (1) it has not been previously allocated by the operating system, or (2) it has been de-allocated. In either situation, its mapping information is discarded, and the system initiates the page allocation process mentioned above. Virtual memory systems can be categorized into two classes: those with fixed-size blocks, called pages, and those with variable-size blocks, called segments.

### 2.3. Caches

The term cache is applied to the techniques buffering reusable data since locality exists in the reference stream. Caching can improve the performance in many computer system levels. Examples include file caches, disk caches, name caches, web caches, etc. Generally, caches in computer architecture refer to the first levels of the memory hierarchy. Caches have been an integral and ever-growing part of modern microprocessors. Approximately half of a modern microprocessor's die area is allocated for caches and the number of transistors dedicated to caches is still growing. They are usually implemented with a number of arrays of SRAM cells because an SRAM cell is superior in terms of performance versus a DRAM cell. Caches also use the same fabrication process as the processor core.

#### 2.3.1. Cache Memory Cell

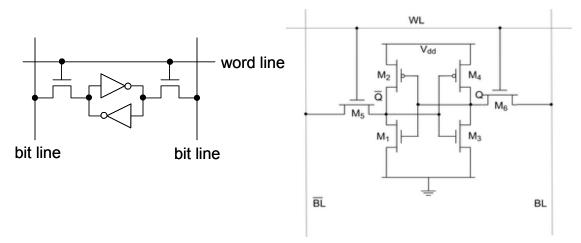

Figure 2.2: The basic SRAM cell--six-transistor memory cell(6T MC).

Figure 2.2 shows the basic SRAM cell, which is an implementation of a six-transistor memory cell (6T MC). This 6T MC cell is connected in a way that it restores the charge back into the memory cell, so the charge does not decrease and the need for refreshing the cell is eliminated. The 6T MC has only one port, which can be used to either read or write a values. When there is a read access, the wordline (WL) is asserted and the voltage difference between the bitline pair is detected. The pair of cross-coupled transistors and the access transistors pull the voltage all the way up to Vdd or down to the ground according to the bit data value. After that, the bitlines are precharged to the original voltage for the next access. In the case of a write, the bitline is driven with a differential voltage from an external source according to the new data to be written. The wordline WL is then asserted and the value that is to be stored is latched into the memory cell. Most conventional designs use this full-CMOS six-transistor memory cell with different variations including sizing, physical layout, and transistor threshold voltages for low power.

#### 2.3.2. Cache Operations

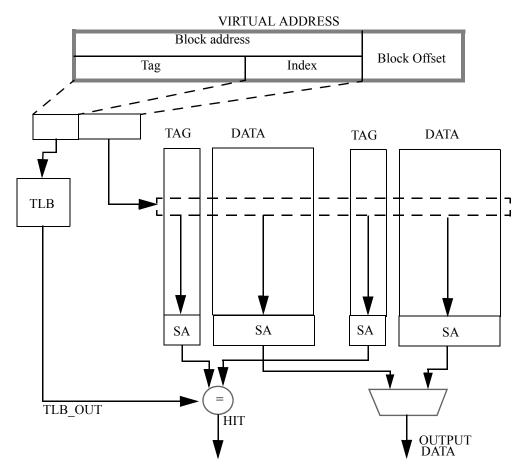

A cache consists of multiple blocks of data. Data blocks are usually organized in a setassociative manner. For example, a cache with four sets and two blocks per set is called twoway set associative. A data block mapped onto a particular set can be freely placed in any of those two blocks in the set. The one-way set associative cache is called a direct-mapped cache and the cache with one set is called fully-associative. Intuitively, more blocks per set translate into more freedom to place the data block to any available blocks in the set, but, as a result, more time and/or power is taken to process the lookup. A cache consists of two arrays, which are the tag array and the data array. The tag array contains an address tag on each block frame that gives the address the data block contains. It also contains a valid bit to identify the validity of the tag entry.

Figure 2.3 shows the read operation to a cache. The virtual address from the processor is divided into virtual page number and page offset. The virtual page number is translated to a physical page address via a page table entry in the TLB. Then, the physical page address is combined with the page offset to produce a physical address. Next, the physical address is divided into tag, index, and block offset. The block offset field selects the desired bytes from the block, the index field selects the set in the cache, and the tag field is compared in parallel against the tags of a selected cache set for a hit. If the address tag is matched with any of the tags from the selected cache set, it is called a cache hit. If it is not a match, it is called a cache miss, and the physical address is forwarded to the next level of memory hierarchy. Note,

Figure 2.3: Block Diagram of a 2-way set associative cache organization,

accessing the cache and address translation at the TLB can be done simultaneously depending on how the virtual address is divided and translated.

The address translation process can be different than the process described above. It depends on whether the virtual address or the physical address is used to tag and index the cache. The virtual address referred to by the processor core is not the same as the physical address which is used to refer to the location physically in memory, so the system requires address translation. Modern processors handle the address translation with the cooperation between the TLB and the operating system. The differences in caches and TLB placement in

the memory hierarchy create different address translation schemes. These different address translation schemes are described below.

The first scheme is physically indexed, physically tagged (PIPT). In PIPT caches, both the tag and index of the cache are in the form of physical addresses. Meaning that the tag and index are identified after the completion of the address translation. Therefore, the TLB lookup process has to be completed before the cache can be accessed, which can slow down the system. However, if the referring page table entry is not a valid entry in the TLB, the system has to access the memory for the entry, translate the address, and then access the cache sequentially. As a result, the benefit of using TLB can be overshadowed by sequential memory accesses for the TLB miss process followed by the actual memory access.

The second scheme is virtually indexed, virtually tagged (VIVT). In VIVT caches, unlike PIPT, both the index and tag are identified from the virtual address directly from the processor without the translation. This VIVT scheme improves the speed of cache access significantly by eliminating the address translation. However, the scheme suffers from several problems, including:

- Care must be taken to changes in TLB entries and changes in address space since virtual address translations usually are changed as part of normal kernel operation. Cache lines must be flushed if the cache lines' translations have changed.

- Cache line Aliasing Problem: multiple virtual addresses may exist for the same physical address, even in a single address space. Each of these virtual addresses should never be in the cache at the same time, even though they represent the same data.

To solve mentioned problems in VIVT, the virtually indexed, physically tagged (VIPT) scheme is introduced. The VIPT scheme can maintain the speed of cache accesses comparable to VIVT. The scheme is as described in the previous section. The index is identified in the virtual address, but the tag is identified in the physical address. VIPT can solve the aliasing problem because the tag refers to the physical address. Therefore, VIPT can detect aliasing when two identical tags exist in the cache. Depending on OS page mapping and shared memory protocol, a VIPT cache can be constructed in such a way that cache-line aliasing will never occur.

Since, in VIPT, the process of cache lookup and TLB lookup can be processed simultaneously, the cache access speed of VIPT is improved versus PIPT. However, the processor can not acknowledge a cache miss until the address translation is complete.

Finally, the last scheme, physically indexed, virtually tagged (PIVT), is basically not used and is not discussed further.

When a cache miss occurs, a block must be selected to be replaced with the referring data. A direct-mapped cache selects the block specified by the address, since there is only one location that the data can go. On the other hand, the set-associative and fully-associative caches have many blocks to select from. There are a number of strategies employed for selecting the block to be replaced, which are collectively called the cache replacement policy. The most common policy is called least-recently used (LRU), which selects the block that has not been accessed for the longest time.

There are two basic options when writing data to the cache, which are write back and write through. Write back writes the data to the block in the cache. The modified cache block is written to a lower level of the memory only when it is replaced. On the other hand, write through writes to both the block in the cache and to the block in the lower-level memory. Since the data are not needed on a write, there are two common options on a write miss, which are write allocate and no-write allocate. Write allocate loads the block to the cache on a write miss, and then restarts the write which causes a write hit. In contrast, no-write allocate does not load the data in the cache, but modifies the block in the lower level where the data is located.

To allow concurrent accesses, a cache can be given multiple ports. Multiported caches can be implemented using different methods. The most common methods are true multiporting and creating multiple independent banks. True multiported caches include additional access transistors for each port, which cause a significant increase in memory area and wire length within the cache. On the other hand, multiple independent banks divide the cache into small banks, where each bank is a simple single-ported cache. Multiple concurrent accesses can be satisfied if the accesses are to different banks. The disadvantage of multiple independent banks is that the cache controller requires additional complexity and intelligence to control each individual bank.

The cache controller functionality includes controlling cache operations and accesses to comply with cache strategies mentioned above. Its function also includes effectively managing other functions, such as multiporting with multiple banks which requires intelligence to control accesses and prevent bank conflicts. Lastly, the cache controller controls the interfacing mechanism to the lower level of memory when a miss occurs. Although caches can be implemented in many different ways, the simple cache implementation described in this section serves as a fundamental cache design. One approach to improve cache performance is to reduce the cache miss rate. All misses can be sorted into three categories: compulsory, capacity, and conflict. Compulsory misses are misses caused by accessing the blocks for the first time. These misses occur to bring the blocks into the cache. Capacity misses are misses due to the limitation in the size of the cache because the cache can not hold all the blocks. Conflict misses are misses caused by multiple blocks mapped to the same set, but the set cannot hold all blocks mapped to it. To reduce the misses, there are three common cache organization strategies: increasing the cache size, increasing the cache associativity, and increasing the block size. While increasing the cache size is a costly fool-proof method, increasing the cache associativity and the block size have their optimal points. Increasing both cache associativity and the block size too aggressively can cause the miss rate to increase.

# **2.3.3.CACTI: An Integrated Cache Timing, Power, and Area Model**

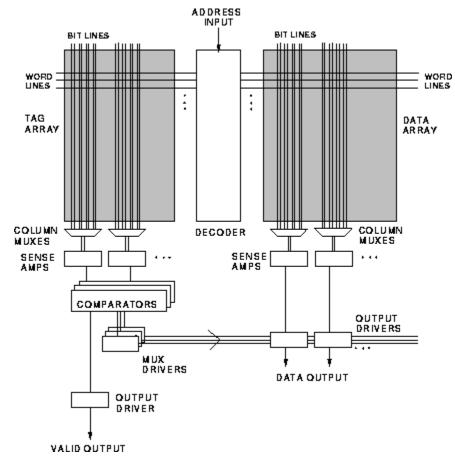

CACTI [12] is a widely-accepted analytical model for the access and cycle times of onchip direct-mapped and set-associative caches. The inputs to the model are the cache size, block size, and associativity, as well as array organization and process parameters. CACTI was originally written by Wilton and Norm Jouppi at DEC WRL. It is available publicly for academic purposes.

Figure 2.4 shows the organization of the SRAM cache being considered in CACTI. First, the decoder decodes the address, then the appropriate row is selected according to the decoded address by driving one wordline in the data array and the corresponding wordline in the tag array. Only one wordline in each array can be asserted at a time. Along the selected

Figure 2.4: Cache structure.

wordline, each memory cell is associated with a pair of bitlines, which are initially precharged high. Then, each memory cell in that row pulls down one of its two bitlines according to the value stored in the memory cell.

Each sense amplifier detects the changes in multiple pairs of bitlines, whose number depends on the layout parameter. The sense amplifier determines the value of the memory cell by detecting which bitline in a pair is pulled down. Multiple pairs of bitlines can share one sense amplifier by inserting a multiplexor before the sense amps. To specify the pair of bitlines to be detected, the select signals from the decoder are fed to the multiplexor. The data from the tag array is compared with the tag bits of the address. The number of comparators required depends on the number of associativity of the cache, for example an N-way set-associative cache requires N comparators. The comparison results, whether a hit or a miss, drive valid output to the output multiplexors. These output multiplexors select the appropriate data from the data array in the case of a set-associative cache or a cache in which the data array is wider than the output width. Additionally, the output multiplexors drive the selected data out of the cache.

Table 2.1 and Table 2.2 show the input and output parameters of CACTI.

| Input<br>Parameter    | Use                                                                       |

|-----------------------|---------------------------------------------------------------------------|

| С                     | Cache size in bytes                                                       |

| В                     | Block size in byes signifying the number of bytes in a single cache entry |

| А                     | Cache associativity                                                       |

| TECH                  | Technology node in micrometers                                            |

| N <sub>subbanks</sub> | Number of cache subbanks                                                  |

| b <sub>0</sub>        | Number of bits of output data                                             |

| b <sub>addr</sub>     | Number of bits of system address                                          |

# Table 2.1: CACTI input parameters

| Output<br>Parameter | Use                                            |

|---------------------|------------------------------------------------|

| N <sub>dwl</sub>    | Number of segmentations of the wordline (Data) |

| N <sub>spd</sub>    | Aspect ratio control parameter (Data)          |

| N <sub>dbl</sub>    | Number of segmentations of the bitline (Data)  |

| N <sub>twl</sub>    | Number of segmentations of the wordline (Tag)  |

| N <sub>tspd</sub>   | Aspect ratio control parameter (Tag)           |

| N <sub>tbl</sub>    | Number of segmentations of the bitline (Tag)   |

#### Table 2.2: CACTI output implementation parameters

CACTI calculates the access and cycle times by estimating delays of the cache components, including:

- decoder

- wordlines (in both the data and tag array)

- bitlines (in both the data and tag array)

- sense amplifiers (in both the data and tag arrays)

- comparators

- multiplexor drivers

- output drivers (data output and valid signal output)

The delay of each of these components is estimated separately and the results combined to estimate the access and cycle time of the entire cache. The delay of each component is estimated by decomposing each component into several equivalent RC circuits, and using simple RC equations to estimate the delay of each stage.

There are two potential critical paths in a cache read access. One is the time to access the tag array and the other is the time to access the data array. The time to read the tag array, perform the comparison, and drive the multiplexor select signals is compared with the time to read the data array. If the former is larger, then the tag array is the critical path. Otherwise, the data array is the critical path. Despite the cache designer's attempts for faster tag path compared with the data path, it is not always possible to do this. Therefore, both sides must be modeled in detail to determine the critical path.

The cycle time is calculated by adding the access time and the precharge delay together. The precharge delay is assumed to be dominated by the wordline fall time and bitline rise time in the data array. The wordline fall time is approximately equal to the wordline rise time and a constant bitline rise time is assumed to be equal to four inverter delays (each with a fan-out of four).

To determine the optimal configuration, CACTI performs an exhaustive search over all combinations of the output parameters corresponding to the specified input parameters. The implementation with the best behavior among all criteria is considered the optimal based on the CACTI's optimization algorithm, which is different for each version of CACTI.

CACTI 2.0 is an extension of the first version of CACTI with support for fullyassociative caches, multiported caches, feature size scaling, and power modeling. The inputs are the cache capacity, associativity, cacheline size, number of read/write ports, and feature size. Its analytical models compute the access time and the energy consumption of the cache for all combinations of possible configurations. The calculation for each configuration divides the data and tag array into smaller subarrays. Finally, CACTI returns the configuration that has the best access time and energy consumption as determined by its optimization function as mentioned above.

The CACTI 2.0 optimizing function takes into account only the access time of the cache and the energy consumption. CACTI 2.0 does not have a concept of the total area or the efficiency (percentage of area occupied by the bits alone) of each configuration. It approximates the wire capacitance and resistance that is associated with the wires in many parts of the cache because it does not have a detailed area model. Additionally, since the optimizing function considers only the access time and the energy consumption, the cache configuration output may not be efficient in area or aspect ratio.

CACTI 3.0 adds a detailed cache area model to CACTI 2.0. CACTI 3.0 calculates the area occupied by each component of the cache for each possible configuration. The model

produces both the efficiency in performance and the aspect ratio of the entire cache for each configuration. To determine the best configuration, the optimizing function considers access time, power consumption, efficiency of the layout, and aspect ratio. The detailed area model accurately calculates the wire lengths and the associated capacitance and resistance of the address and data routing tracks. This results in more realistic power estimates. Finally, CACTI 3.0 also supports fully independent banking of caches.

# 2.3.4. Wattch

Wattch [19] is a framework for analyzing and optimizing microprocessor power dissipation at the architecture-level. Wattch is claimed to be 1000 times or more faster than existing layout-level power tools, and yet maintains accuracy within 10% of their estimates as verified by using industry tools on leading-edge designs. It provides a power evaluation methodology within the popular SimpleScalar framework. Since, in this dissertation, Wattch is used as a power estimation tool for caches, this section will discuss Wattch only in the context of cache power estimation.

Wattch calculates the dynamic power consumption  $(P_d)$  as:

$$P_d = C V_{dd}^2 a f$$

where

C is the load capacitance,

$V_{dd}$  is the supply voltage,

f is the clock frequency, and

*a* is the activity factor.

The activity factor a is a fraction between 0 and 1 that represents the average switching activity on each clock cycle. Wattch estimates C based on the circuit and the transistor sizing as described below. *Vdd* and f depend on the assumed process technology as defined in the header file power.h. The user can choose among 0.10, 0.18, 0.25, 0.35, 0.40, and 0.80 micron technology, and Wattch will automatically resize the transistor accordingly.

Wattch calculates the power consumption based on only the capacitance of each stage, rather than both R and C. Additionally, Wattch analyzes and sums the power consumption of all paths, not only the critical path. In Wattch, certain critical transistors are automatically sized based on the model parameters to achieve reasonable delays.

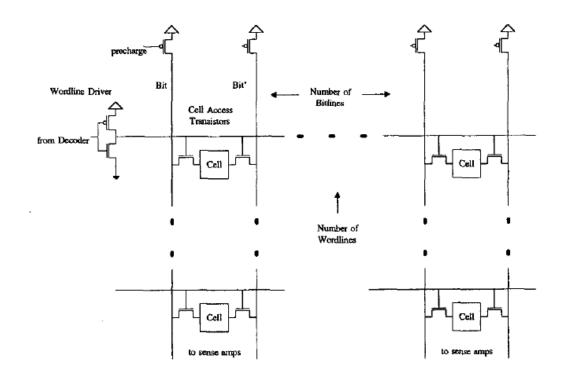

Figure 2.5: Schematic of wordlines and bitlines in Wattch array structure [19].

A cache in Wattch was implemented as an array structure. The power model of the cache is based on the number of rows, columns, and the number of read/write ports. These parameters affect the size and number of decoders, the number of wordlines, and the number of bitlines. In addition, these parameters are used to estimate the length of the pre-decode wires and the lengths of the array's wordlines and bitlines. The wordline and bitline capacitance are computed in a similar way. The wordline capacitance includes the capacitance of the wordline driver, the gate capacitance of the cell access transistor multiplied by the number of bitlines, and the capacitance of the wordline's metal wire. The bitline capacitance includes the diffusion capacitance of the pre-charge transistor, the diffusion capacitance of the cell access transistor multiplied by the number of word lines, and the metal capacitance of the bitline. The number of ports also affects the power consumption due to additional transistor connections on wordlines, two additional bitlines, and longer wires on both wordlines and bitlines.

Wattch authors estimate the physical implementations for cache structures using the help of the CACTI tools [12]. As described in the previous section, CACTI takes the cache size, block size and associativity as inputs, and chooses the organization that gives the smallest access time.

Wattch considers three different options for clock gating to disable unused resources in a multi-ported cache.

- 1. *All-or-nothing approach*. The full modeled power will be consumed if any accesses occur in a given cycle, and zero power consumption otherwise.

- 2. *Scaled linearly*. If only a portion of a cache's ports are accessed, the power is scaled linearly with the number of accessed port(s).

3. *Scaled linearly with 10 per cent*. It is the same as the second option except that unused units dissipate 10% of their maximum power, rather than drawing zero power.

To interface with SimpleScalar, the Wattch power model tracks which units are accessed on each cycle and how. The power model also varies the estimated power based on the number of ports used and which clock-gating scheme is used.

# 2.4. Main Memory: DRAM